## UNIVERSIDAD NACIONAL DEL CALLAO FACULTAD DE INGENIERÍA ELÉCTRICA Y ELECTRÓNICA ESCUELA PROFESIONAL DE INGENIERÍA ELECTRÓNICA

"DISEÑO E IMPLEMENTACIÓN DE UN GENERADOR DE SEÑALES

DE RADIOFRECUENCIA BASADO EN FPGA SoC PARA LA

OPERACIÓN DE UN TRANSMISOR DE RADAR IONOSONDA EN EL

RADIO OBSERVATORIO DE JICAMARCA"

## TESIS PARA OPTAR EL TÍTULO PROFESIONAL DE INGENIERO ELECTRÓNICO

Autor : B.Sc. Brayan Lui Estalla Quinteros

Asesor : M.Sc. Jaime Alberto Vallejos Laos

Co-asesor : Dr. Marco Antonio Milla Bravo

Línea de Investigación : Ingeniería Y Tecnología

Callao – 2024

PERÚ

### Tesis\_Brayan Lui Estalla Quinteros

14% Textos sospechosos

#### 1 4% Similitudes

< 1% similitudes entre comilias 0% entre las fuentes mencionadas

11% Idiomas no reconocidos

Nombre del documento: Tesis\_Brayan Lui Estalla Quinteros.pdf ID del documento: bca97d96cb2b0713012bddeb1abe7e451edba11a Tamaño del documento original: 13,58 MB **Depositante:** FIEE PREGRADO UNIDAD DE INVESTIGACION

Fecha de depósito: 21/3/2024

Tipo de carga: interface

fecha de fin de análisis: 21/3/2024

Número de palabras: 22.907 Número de caracteres: 169.509

Ubicación de las similitudes en el documento:

#### ≡ Fuentes de similitudes

#### Fuentes principales detectadas

| N° |   | Descripciones                                                                                                        | Similitudes | Ubicaciones | Datos adicionales                                  |

|----|---|----------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------------------------------------------|

| 1  | 8 | unac.edu.po https://unac.edu.pe/wp-content/uploads/documentos/transparencia/articulo-11/11-2/transparencia           | 2%          |             | 🖺 Palabras idénticas: <b>2%</b> (431 palabras)     |

| 2  | 8 | repositorio.ues.edu.sv<br>https://repositorio.ues.edu.sv/bitstreams/3a9a94da-8178-4b34-9fc4-1bfe7ae6f3a6/download    | <1%         |             | Ĉ Palabras idénticas: < 1% (149 palabras)          |

| 3  | 8 | oa.upm.es<br>https://oa.upm.es/47722/1/JHON_JAIRO_BARONA_MENDOZA.pdf<br>1 fuente similar                             | < 1%        |             | Ĉ Palabras idénticas: <b>&lt; 1%</b> (97 palabras) |

| 4  | 8 | <b>ru.dgb.unam.mx</b><br>https://ru.dgb.unam.mx/bitstream/20.500.14330/TES01000617587/3/0617587.pdf                  | <1%         |             | Ĉ∩Palabras idénticas: <b>&lt; 1%</b> (90 palabras) |

| 5  | 8 | revistatelematica.cujae.edu.cu<br>https://revistatelematica.cujae.edu.cu/index.php/tele/article/download/103/102/307 | <1%         |             | Ĉ Palabras idénticas: <b>&lt; 1%</b> (80 palabras) |

#### **Fuentes con similitudes fortuitas**

| N° |   | Descripciones                                                                                                                  | Similitudes | Ubicaciones | Datos adicionales                                   |

|----|---|--------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-----------------------------------------------------|

| 1  | • | INFORME FINAL DE TESIS (1).pdf   INFORME FINAL DE TESIS (1) #2b4a0f<br>◆ El documento proviene de mi biblioteca de referencias | < 1%        |             | Ĉ Palabras idénticas: < 1% (26 palabras)            |

| 2  | 8 | abacoenred.com<br>https://abacoenred.com/wp-content/uploads/2019/02/El-proyecto-de-investigación-F.GArias-2012                 | < 1%        |             | Ĉ Palabras idénticas: < 1% (25 palabras)            |

| 3  | 8 | www.ltq.edu.mx http://www.itq.edu.mx/carreras/IngElectronica/archivos_contenido/Apuntes de materias/Apuntes_V                  | < 1%        |             | Ĉ Palabras idénticas: <b>&lt; 1</b> % (18 palabras) |

| 4  | 8 | ru.dgb.unam.mx<br>https://ru.dgb.unam.mx/bitstream/20.500.14330/TES01000678100/3/0678100_A1.pdf                                | < 1%        |             | 🖒 Palabras idénticas: < 1% (15 palabras)            |

| 5  | 8 | Inaoe.repositorioinstitucional.mx<br>https://inaoe.repositorioinstitucional.mx/jspui/bitstream/1009/2028/1/RicardezTMR.pdf     | < 1%        |             | Ĉ Palabras idénticas: <b>&lt; 1%</b> (18 palabras)  |

#### Fuentes mencionadas (sin similitudes detectadas) Estas fuentes han sido citadas en el documento sin encontrar similitudes.

- 1 X http://jro.igp.gob.pe/digisonde/dps4text.htm

- $2 \hspace{0.2cm} \nearrow\hspace{0.2cm} \texttt{Mttp://www.digisonde.com/pdf/Digisonde4DManual\_LDI-web.pdf} \\$

- 3 kttps://redpitaya.com/

| INFORMACIÓN BÁSICA         |                                                                                                                                                                                                    |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FACULTAD                   | FACULTAD DE INGENIERÍA ELÉCTRICA Y ELECTRÓNICA                                                                                                                                                     |  |

| UNIDAD DE<br>INVESTIGACIÓN | DE LA FACULTAD DE INGENIERÍA ELÉCTRICA Y<br>ELECTRÓNICA                                                                                                                                            |  |

| TÍTULO                     | "DISEÑO E IMPLEMENTACIÓN DE UN GENERADOR DE<br>SEÑALES DE RADIOFRECUENCIA BASADO EN FPGA SoC<br>PARA LA OPERACIÓN DE UN TRANSMISOR DE RADAR<br>IONOSONDA EN EL RADIO OBSERVATORIO DE<br>JICAMARCA" |  |

| AUTOR                      | <ul> <li>B.Sc. ESTALLA QUINTEROS BRAYAN LUI</li> <li>CÓDIGO ORCID: 0000-0001-8897-0367</li> <li>DNI: 76658936</li> </ul>                                                                           |  |

| ASESOR                     | ❖ M.Sc JAIME ALBERTO VALLEJOS LAOS                                                                                                                                                                 |  |

| CO-ASESOR                  | <ul> <li>CÓDIGO ORCID: 0000-0003-4519-4657</li> <li>DNI: 08786103</li> <li>Dr. MARCO ANTONIO MILLA BRAVO</li> <li>CÓDIGO ORCID: 0000-0001-9067-863X</li> <li>DNI: 09860554</li> </ul>              |  |

| LUGAR DE<br>EJECUCIÓN    | RADIO OBSERVATORIO DE JICAMARCA                                                                         |

|--------------------------|---------------------------------------------------------------------------------------------------------|

| UNIDADES DE<br>ANÁLISIS  | PARÁMETROS DE OPERACIÓN DE UN TRANSMISOR DE<br>RADAR IONOSONDA EN EL RADIO OBSERVATORIO DE<br>JICAMARCA |

| TIPO DE<br>INVESTIGACIÓN | TIPO APLICADA, DISEÑO EXPERIMENTAL, NIVEL EXPLICATIVO, ENFOQUE CUANTITATIVO                             |

| TEMA OCDE                | INGENIERÍA Y TECNOLOGÍA                                                                                 |

# UNIVERSIDAD NACIONAL DEL CALLAO FACULTAD DE INGENIERÍA ELÉCTRICA Y ELECTRÓNICA ACTA PARA LA OBTENCIÓN DEL TÍTULO PROFESIONAL POR LA MODALIDAD DE TESIS SIN CICLO DE TESIS

Al día 04 del mes de junio de 2024 siendo las 11:00 horas se reunió el Jurado Examinador de la Facultad de Ingeniería Eléctrica y Electrónica de la Universidad Nacional del Callao, aprobada mediante Resolución Decanal N°126-2024-DFIEE, conformado por los siguientes docentes ordinarios:

Dr. Ing. JACOB ASTOCONDOR VILLAR

M. Sc. Ing. JULIO CESAR BORJAS CASTAÑEDA

Dr. Ing. FERNANDO MENDOZA APAZA

Dr. Ing. ABILIO BERNARDINO CUZCANO RIVAS

Presidente

Secretario

Vocal

Suplente

Asimismo se dio inicio a la exposición de TESIS del señor Bachiller ESTALLA QUINTEROS, Brayan Lui; quienes habiendo cumplido con los requisitos para obtener el Título Profesional en Ingeniería Electrónica como lo señalan los Arts. N°s 08 al 10 del Reglamento de Grados y Títulos, sustentará la Tesis Titulada: "DISEÑO E IMPLEMENTACIÓN DE UN GENERADOR DE SEÑALES DE RADIOFRECUENCIA BASADO EN FPGA SoC PARA LA OPERACIÓN DE UN TRANSMISOR DE RADAR IONOSONDA EN EL RADIO OBSERVATORIO DE JICAMARCA" con el quórum Reglamentario de Ley, se dio inicio a la exposición, considerando lo establecido en el Art. N° 80 del Reglamento de Grados y Títulos dado por Resolución N° 150-23-CU, en el Sub Capítulo II, corresponde al otorgamiento del Título Profesional con Tesis sin Ciclo de Tesis, efectuadas las deliberaciones pertinentes se acordó:

Dar por AP POBADO...... Calificativo HVY BUENO... nota: 18 al expositor ESTALLA QUINTEROS, Brayan Lui; con lo cual se dio por concluida la sesión, siendo las... 12:00...... horas del día del mes y año en curso.

Es copia fiel del folio N° 261 del Libro de Actas de Sustentación de Tesis de la Facultad de Ingeniería Eléctrica y Electrónica – UNAC.

Dr. Ing. JACOB ASTOCONDOR VILLAR PRESIDENTE

VI. Sc. Ing. JULIO CESAR BORJAS CASTAÑEDA SECRETARIO

Dr. Ing. FERNANDO MENDOZA APAZA VOCAL

Dr. Ing. ABILIO BERNARDINO CUZCANO RIVAS

SUPLENTE

#### INFORME FAVORABLE

EL PRESIDENTE DEL JURADO EVALUADOR DE SUSTENTACIÓN DE TESIS DE LA ESCUELA PROFESIONAL DE INGENIERÍA ELECTRÓNICA DE LA FACULTAD DE INGENIERÍA ELÉCTRICA Y ELECTRÓNICA DE LA UNIVERSIDAD NACIONAL DEL CALLAO; que suscribe:

Deja constancia de que el día martes 04 de junio de 2024, el señor Bachiller en Ingeniería Electrónica ESTALLA QUINTEROS, Brayan Lui; quien habiendo cumplido con los requisitos establecidos en la normativa, sustento la Tesis titulada: "DISEÑO E IMPLEMENTACIÓN DE UN GENERADOR DE SEÑALES DE RADIOFRECUENCIA BASADO EN FPGA SoC PARA LA OPERACIÓN DE UN TRANSMISOR DE RADAR IONOSONDA EN EL RADIO OBSERVATORIO DE JICAMARCA", habiendo obtenido la nota de 18 (dieciocho), según el folio 261 del Libro de Actas de Sustentación.

Se extiende el presente en cumplimiento de lo establecido en el Reglamento de Grados y Títulos de Pregrado de la Universidad Nacional del Callao.

Callao, 04 de junio de 2024

DR. ING. JACOB ASTOCONDOR VILLAR Presidente del Jurado Evaluador

#### **DEDICATORIA**

A Dios por guiarme siempre, a mis padres Guisela Quinteros y Luis Estalla, a mis hermanos Luis, Cristhian, Vicente y Jazmin quienes me apoyaron incondicionalmente, a Jhassmin por siempre alentarme en todo momento.

#### **AGRADECIMIENTO**

A mi madre Guisela Quinteros que siempre estuvo en todo momento alentándome, al Dr. Edgar del Aguila por su amistad, consejos brindados y siempre motivarme a investigar e inventar. Al M.Sc. Jaime Vallejos por sus enseñanzas en mi etapa universitaria y el apoyo brindado como asesor.

Al Dr. Marco Milla de quien estoy agradecido por la confianza puesta en mí al desarrollar esta investigación, paciencia y conocimientos brindados. Al BSc. Joaquín Verástegui por los grandes momentos compartidos en el laboratorio de IDI y compartir conmigo esa pasión por el hardware y FPGA's

A Jhassmin por su amor, confiar en mí y bellos momentos compartidos.

## ÍNDICE

| ÍNDICE DE FIGURAS                             | 13 |

|-----------------------------------------------|----|

| ÍNDICE DE TABLAS                              | 20 |

| RESUMEN                                       | 21 |

| ABSTRACT                                      | 22 |

| INTRODUCCIÓN                                  | 23 |

| I.PLANTEAMIENTO DEL PROBLEMA                  | 24 |

| 1.1. Descripción de la realidad problemática  | 24 |

| 1.2. Formulación del problema                 | 25 |

| 1.2.1. Problema general                       | 25 |

| 1.2.2. Problemas específicos                  | 25 |

| 1.3. Objetivos                                | 25 |

| 1.3.1. Objetivos generales                    | 25 |

| 1.3.2. Objetivos específicos                  | 26 |

| 1.4. Justificación                            | 26 |

| 1.4.1. Justificación Teórica                  | 26 |

| 1.4.2. Justificación Práctica                 | 27 |

| 1.4.3. Justificación Metodológica             | 27 |

| 1.4.4. Justificación Social                   | 27 |

| 1.5. Limitaciones de la investigación         | 28 |

| 1.5.1. Limitación teórica                     | 28 |

| II. MARCO TEÓRICO                             | 29 |

| 2.1. Antecedentes: Internacional y nacionales | 29 |

| 2.1.1. Antecedentes internacionales           | 29 |

| 2.1.2. Antecedentes nacionales                | 30 |

| 2.2. Bases teóricas                           | 31 |

| 2.2.1. Ionósfera                              | 31 |

| 2.2.2. Radar ionosonda                        | 32 |

|      | 2.2.3. Rango, resolución y ecuación del radar          | 34 |

|------|--------------------------------------------------------|----|

|      | 2.2.4. lonograma                                       | 37 |

|      | 2.2.5. Matrices de puertas programables por campo FPGA | 38 |

|      | 2.2.6. Red Pitaya SIGNAL lab 250-12                    | 39 |

|      | 2.2.7. Lenguaje de descripción de hardware (VHDL)      | 40 |

|      | 2.2.8. Niveles de abstracción                          | 40 |

|      | 2.2.9. Estilos de descripción de hardware              | 41 |

|      | 2.3. Marco conceptual                                  | 43 |

|      | 2.3.1. Controlador de radar                            | 43 |

|      | 2.3.2. Oscilador controlado numéricamente (NCO)        | 44 |

|      | 2.3.3. Modulación BPSK                                 | 46 |

|      | 2.3.4. Modulación OOK                                  | 48 |

|      | 2.4. Definición de términos básicos                    | 49 |

| III. | HIPOTESIS Y VARIABLES                                  | 51 |

|      | 3.1. Hipótesis general e hipótesis específicas         | 51 |

|      | 3.1.1. Hipótesis general                               | 51 |

|      | 3.1.2. Hipótesis específicas                           | 51 |

|      | 3.2. Definición conceptual de variables                | 51 |

|      | 3.2.1. Variable independiente                          | 51 |

|      | 3.2.2. Variable dependiente                            | 52 |

|      | 3.3. Operacionalización de variables                   | 53 |

|      | 3.3.1. Variable independiente                          | 53 |

|      | 3.3.2. Variable dependiente                            | 53 |

| IV.  | DISEÑO METODOLÓGICO                                    | 56 |

|      | 4.1. Tipo y diseño de investigación                    | 56 |

|      | 4.1.1. Tipo de investigación                           | 56 |

|      | 4.1.2. Diseño de investigación                         | 56 |

|      | 4.1.3. Nivel de investigación                          | 56 |

|          | 4.1.4. Enfoque de la investigación: cuantitativo                     | 56 |

|----------|----------------------------------------------------------------------|----|

|          | 4.2. Método de investigación                                         | 57 |

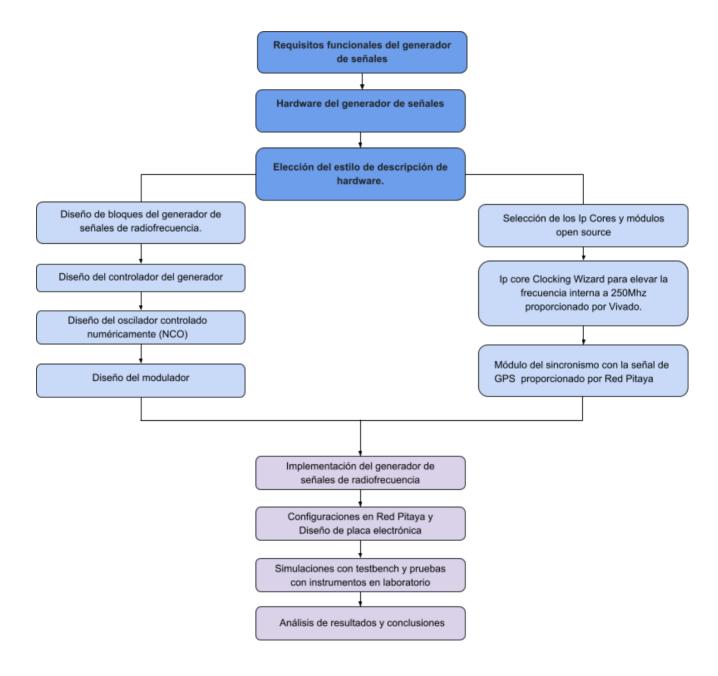

|          | 4.2.1 Diagrama de la metodología                                     | 58 |

|          | 4.2.2. Requisitos funcionales del generador de señales               | 59 |

|          | 4.2.3. Diseño de bloques del generador de señales de radiofrecuencia |    |

|          | 60                                                                   |    |

|          | 4.2.4. Diseño del controlador SPI                                    | 60 |

|          | 4.2.5. Diseño de bloques de Numerically Controlled Oscillator (NCO)  | 62 |

|          | 4.2.6. Cálculos para el acumulador de fase                           | 63 |

|          | 4.2.7. Hardware para el generador de radiofrecuencias                | 64 |

|          | 4.2.8. Elección del estilo de descripción de hardware                | 65 |

|          | 4.2.9. Implementación del módulo de sincronismo                      | 65 |

|          | 4.2.10. implementación del generador de señales de radiofrecuencia.  | 67 |

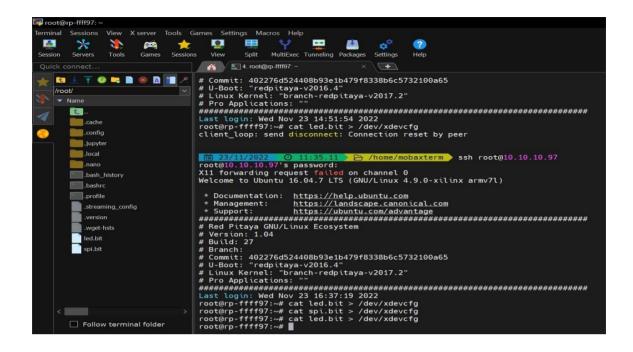

|          | 4.2.11. Configuraciones en Red Pitaya                                | 67 |

|          | 4.2.12. Diseño de placa electrónica                                  | 70 |

|          | 4.2.13. Simulación con el test bench                                 | 77 |

|          | 4.2.14. Pruebas con los instrumentos de laboratorio                  | 77 |

|          | 4.3. Población y muestra                                             | 77 |

|          | 4.3.1. Población                                                     | 77 |

|          | 4.3.2. Muestra                                                       | 77 |

|          | 4.4. Lugar de estudio                                                | 78 |

|          | 4.5. Técnicas e instrumentos para la recolección de datos            | 78 |

|          | 4.6. Análisis y procesamiento de datos                               | 80 |

| <b>.</b> | RESULTADOS                                                           | 87 |

|          | 5.1. Resultados descriptivos                                         | 87 |

|          | 5.1.1. Resultados de la simulaciones                                 | 87 |

|          | 5.1.2. Resultados de la implementación del Generador de señales de   |    |

|          | radiofrecuencia                                                      | 91 |

|          |                                                                      |    |

| 5. I. Z. I. Resultados de la Implementación de la tarjeta electron   | ıca9 ı  |

|----------------------------------------------------------------------|---------|

| 5.1.2.2. Resultados de la implementación del Rack                    | 92      |

| 5.1 3. Cargar el archivo Bitstream en la Red Pitaya Signal Lab 250   | )-12.94 |

| 5.1.4. Sincronismo de radar                                          | 95      |

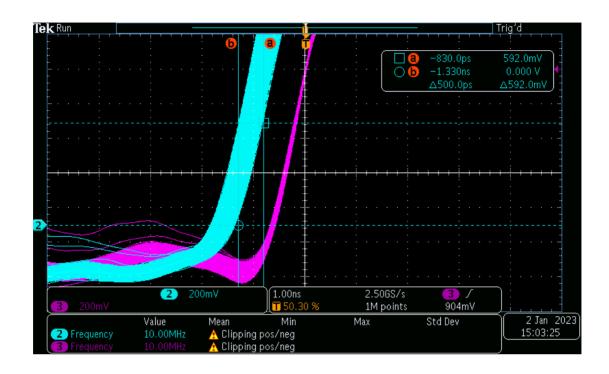

| 5.1.4.1. Sincronismo de la señal de clock de GPS y clock gene        | erado   |

| por generador de señales de radiofrecuencia                          | 95      |

| 5.1.4.2. Comparación de la señal de clock de GPS y clock gen         | erada   |

| por sistema con persistencia                                         | 96      |

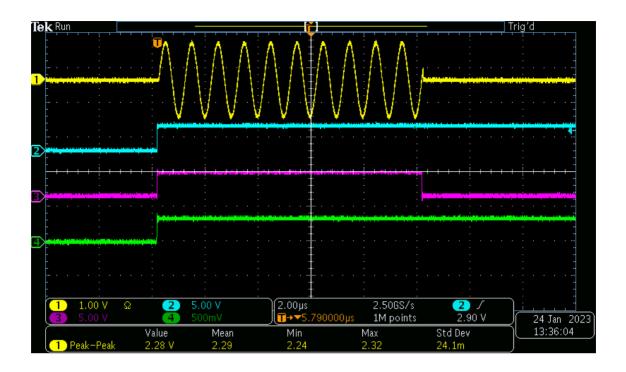

| 5.1.5 Análisis de la generación de señales de radiofrecuencia        | 97      |

| 5.1.5.1. Análisis en el tiempo de la generación de señales de        |         |

| radiofrecuencia                                                      | 97      |

| 5.1.5.2. Análisis espectral de la generación de señales de           |         |

| radiofrecuencia                                                      | 107     |

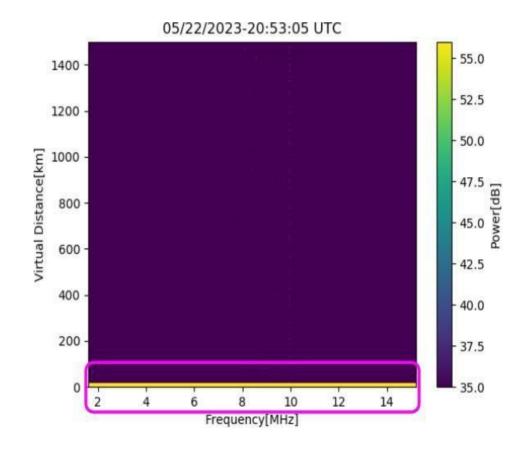

| 5.1.6. Resultados de Prueba Bola de Cobre                            | 110     |

| 5.1.6.1. lonograma de la recepción señales en la prueba bola         |         |

| cobre                                                                | 120     |

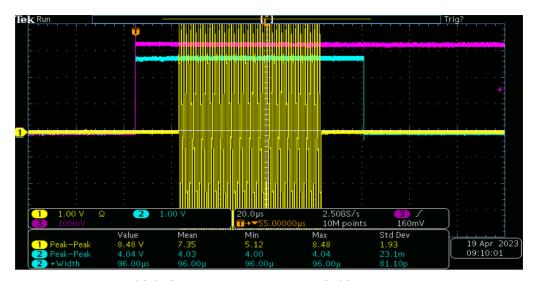

| 5.1.7. Operación del Generador de RF con transmisor de 4KW           | 121     |

| 5.1.7.2. Sondeo oblicuo ionosféricos                                 | 128     |

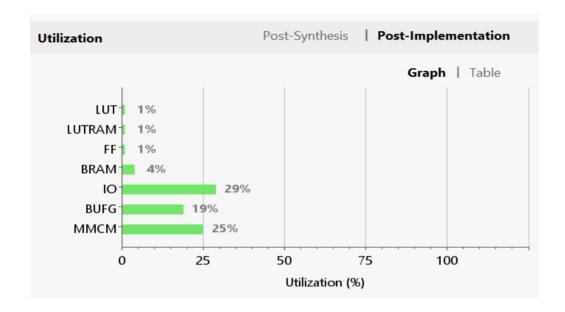

| 5.1.8. Recursos lógicos utilizados                                   | 133     |

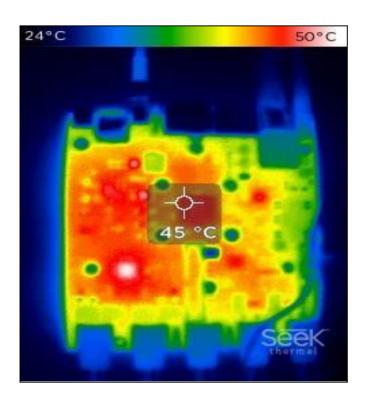

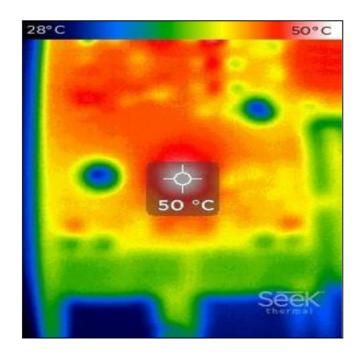

| 5.1.9. Temperatura de operación                                      | 133     |

| VI. DISCUSIÓN DE RESULTADOS                                          | 135     |

| 6.1. Contrastación y demostración de la hipótesis con los resultados | 135     |

| 6.1.1. Contrastación y demostración de la hipótesis general con lo   | S       |

| resultados                                                           | 135     |

| 6.1.2. Contrastación y demostración de las hipótesis específicas o   | on los  |

| resultados                                                           | 135     |

| 6.2 Responsabilidad ética de acuerdo a los reglamentos vigentes      | 136     |

| VII. CONCLUSIONES                                                    | 137     |

| VIII. RECOMENDACIONES                                                | 138     |

| IX. | REFERENCIAS BIBLIOGRÁFICAS                                         | .139 |

|-----|--------------------------------------------------------------------|------|

| X.  | ANEXOS                                                             | .141 |

|     | 8.1. Matriz de consistencia                                        | .141 |

|     | 8.2. Registros de frecuencias                                      | .142 |

|     | 8.3. Registros de ancho de pulso y baudios                         | .144 |

|     | 8.4. Registros de ancho del IPP                                    | .145 |

|     | 8.5. Código .ino del microcontrolador Seeeduino XIAO               | .146 |

|     | 8.6. Código .h del microcontrolador Seeeduino XIAO                 | .151 |

|     | 8.7. Código VHDL del módulo spi controller                         | .152 |

|     | 8.8. Código VHDL del módulo memory controller                      | .158 |

|     | 8.9. Código VHDL del módulo oscilador controlado numéricamente (NC | O)   |

|     | 166                                                                |      |

|     | 8.10. Código VHDL del módulo Tabla de búsqueda del seno(0º) y      |      |

|     | seno(180º)                                                         | .169 |

|     | 8.11. Código VHDL del módulo delay para la Tabla de búsqueda del   |      |

|     | seno(0º) y seno(180º)                                              | .173 |

|     | 8.12. Código VHDL del módulo Modulador OOK - BPSK                  | .175 |

|     | 8.13. Código VHDL del módulo Multiplexor                           | .182 |

|     | 8.14. Código Verilog del módulo de sincronismo                     | .185 |

## **ÍNDICE DE FIGURAS**

| Fig. 1. Sistema digisonda DPS-4 [8]                                     | 33 |

|-------------------------------------------------------------------------|----|

| Fig. 2. Antena transmisora delta cruzada simple del sistema DPS-4 [16]. | 33 |

| Fig. 3. Una de las 4 antenas receptoras del sistema DPS-4 [16]          | 34 |

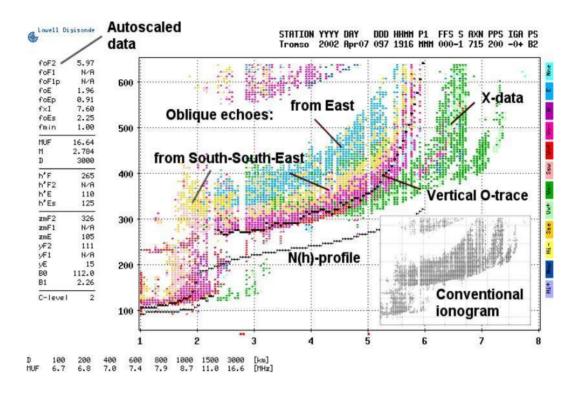

| Fig. 4. lonograma escalado automáticamente con software ARTIST4 [8]     | 38 |

| Fig. 5. Tarjeta de evaluación Red Pitaya SIGNAL lab 250-12 [10]         | 39 |

| Fig. 6. Descripción comportamental de un multiplexor                    | 41 |

| Fig. 7. Descripción del flujo de datos de un multiplexor                | 42 |

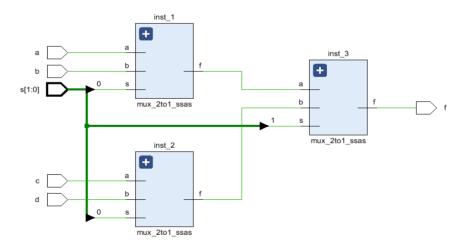

| Fig. 8. Descripción estructural de un multiplexor                       | 42 |

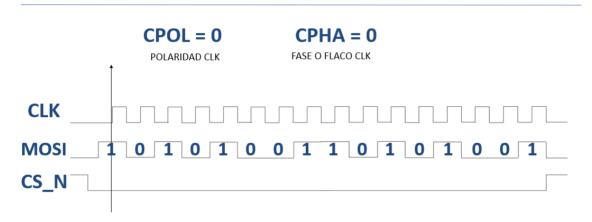

| Fig. 9. Protocolo de comunicación SPI                                   | 43 |

| Fig. 10. Diagrama de bloque del NCO [12]                                | 45 |

| Fig. 11. Modulación por código de desplazamiento de fase (BPSK) [14]    | 47 |

| Fig. 12. Modulación de desplazamiento de amplitud binario (OOK) [13]    | 48 |

| Fig. 13. Diagrama de la metodología                                     | 58 |

| Fig. 14. Diseño de bloques del generador de radiofrecuencias            | 60 |

| Fig. 15. Diseño de bloques de Numerically Controlled Oscillator (NCO)   | 62 |

| Fig. 16. Hardware del generador de señales de radiofrecuencia           | 65 |

| Fig. 17. Conexiones del circuito de sincronismo                         | 66 |

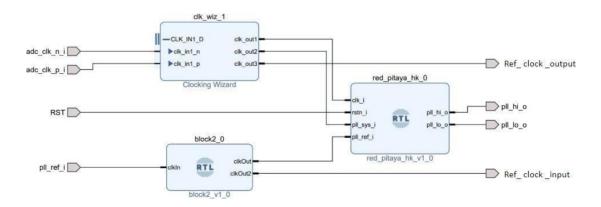

| Fig. 18. Diseño de bloques del circuito de sincronismo en Vivado        | 66 |

| Fig. 19. Diseño de bloques del circuito de sincronismo en Vivado        | 67 |

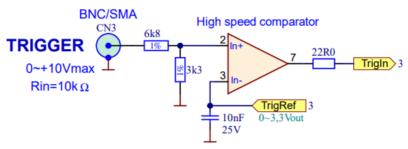

| Fig. 20. Señal de trigger conectada al High speed comparator [10]       | 68 |

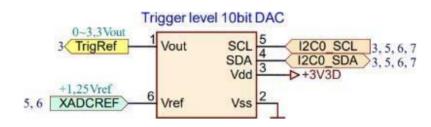

| Fig. 21. Trigger level de 10 bit Dac - mcp 4716 [10]                    | 68 |

| Fig. 22. Programación del mcp 4716                                      | 68 |

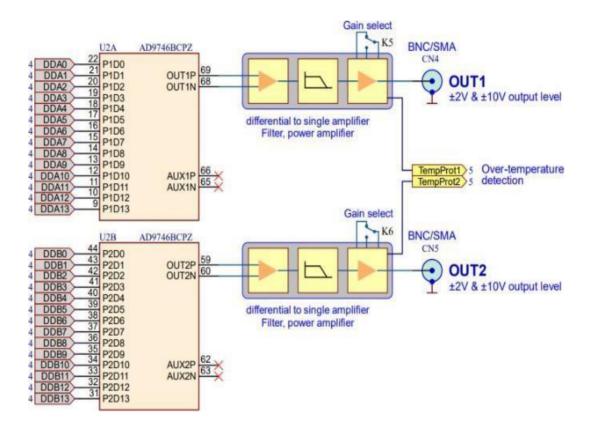

| Fig. 23. DAC-AD9746BCPZ de 14 bits conectados a los relés [10]          | 69 |

| Fig. 24. Programación del expansor MAX 7311                             | 70 |

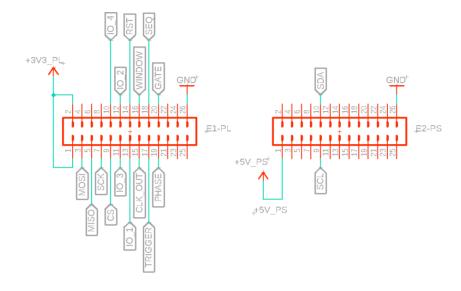

| Fig. 25. Conexiones de los GPIOs del PL y PS                            | 72 |

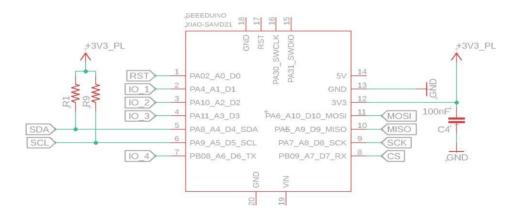

| Fig. 26. Conexiones del Seeeduino Xiao                                  | 72 |

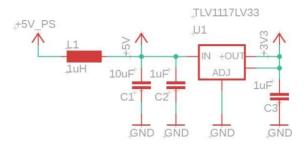

| Fig. 27. Conexiones del regulador lineal de baja caída TLV1117LV            | 73  |

|-----------------------------------------------------------------------------|-----|

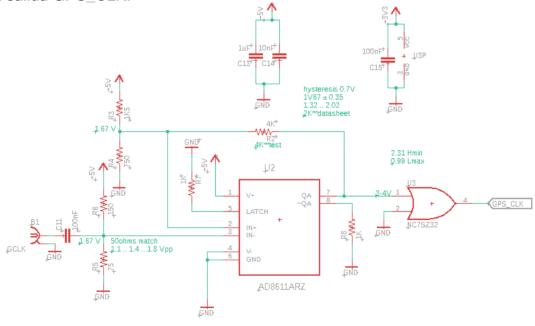

| Fig. 28. Conexiones del comparador de alta velocidad AD8611                 | 73  |

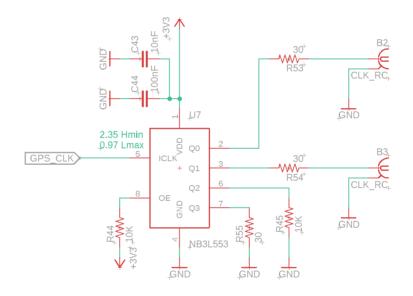

| Fig. 29. Conexiones del circuito de distribución de clock                   | 74  |

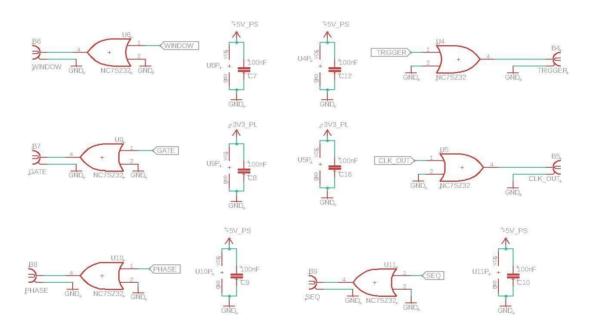

| Fig. 30. Conexiones de las salidas del PL hacia los conectores BNC y SN 75  | ΊA. |

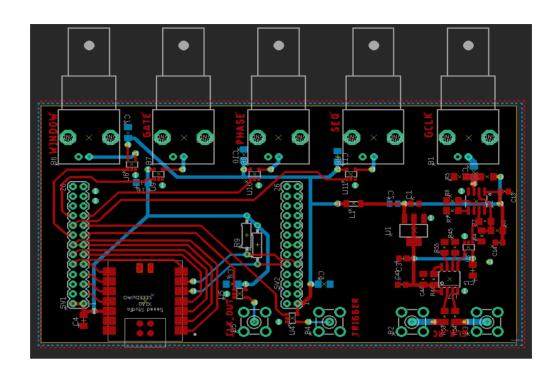

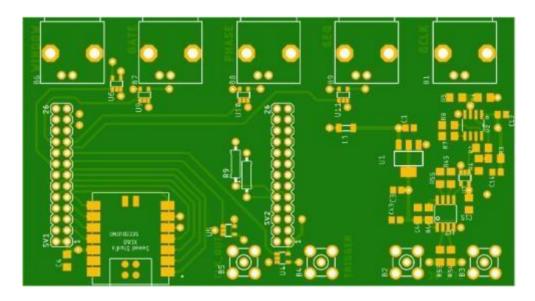

| Fig. 31. Ruteo de pista de placa electrónica en software Eagle              | 76  |

| Fig. 32. Diseño final de la placa electrónica visualizado desde el software |     |

| fusion 360.                                                                 | 76  |

| Fig. 33. Osciloscopio TEKTRONIK MDO3054 - 500Mhz                            | 78  |

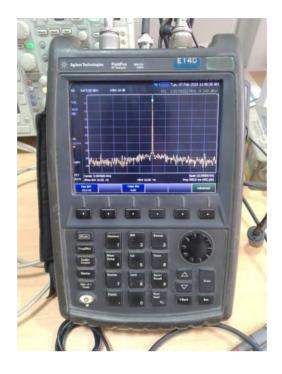

| Fig. 34. Analizador de espectro Agilent Technologies N9912A - 4Ghz          | 79  |

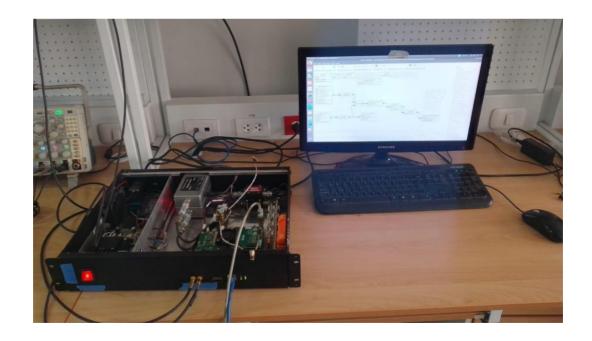

| Fig. 35. Receptor de radar ionosonda IER basado en USRP                     | 79  |

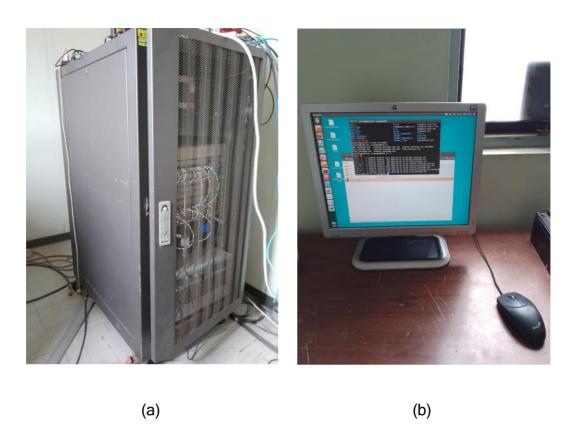

| Fig. 36. Receptor del radar ionosonda VIPIR. (a) Gabinete, (b)              |     |

| Computadora                                                                 | 80  |

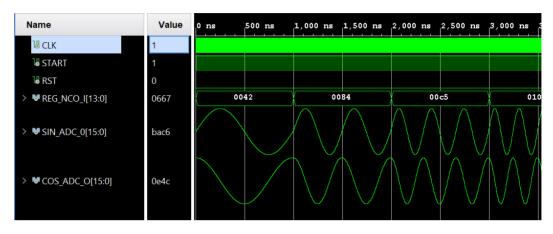

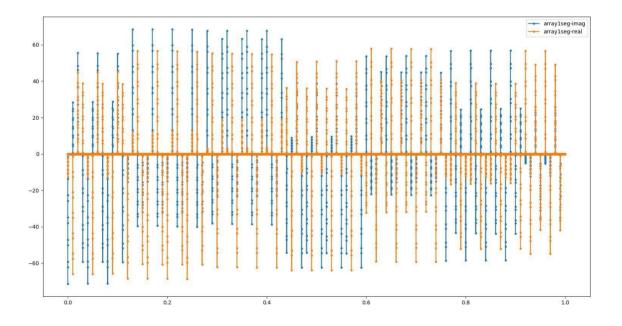

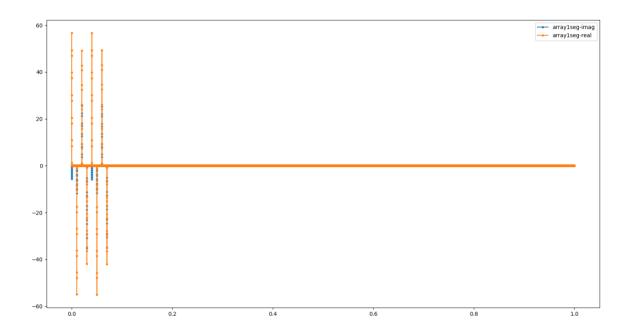

| Fig. 37. Gráfico de simulaciones con banco de pruebas (test bench)          | 81  |

| Fig. 38. Gráficos de la generación de señales con osciloscopio              |     |

| TEKTRONIK                                                                   | 81  |

| Fig. 39. Gráficos del análisis espectral en frecuencia                      | 82  |

| Fig. 40. Receptor y antena de GPS de la marca TRIMBLE                       | 82  |

| Fig. 41. Prueba de bola de cobre                                            | 83  |

| Fig. 42. Estructura interna del Radar ionosonda VIPIR (Generador de         |     |

| señales de radiofrecuencia, etapa de potencia, receptor de ecos             |     |

| ionosféricos)                                                               | 84  |

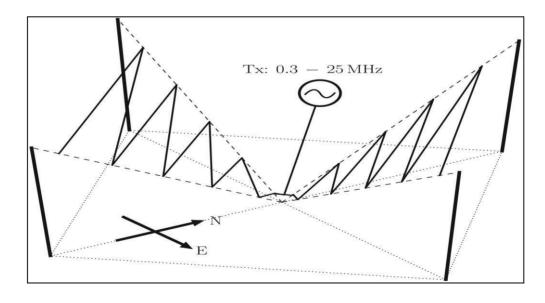

| Fig. 43. Diagrama de Antena logarítmica periódica de banda ancha del        |     |

| transmisor de Radar ionosonda VIPIR [15]                                    | 84  |

| Fig. 44. Antena logarítmica periódica de banda ancha del transmisor de      |     |

| Radar ionosonda VIPIR                                                       | 85  |

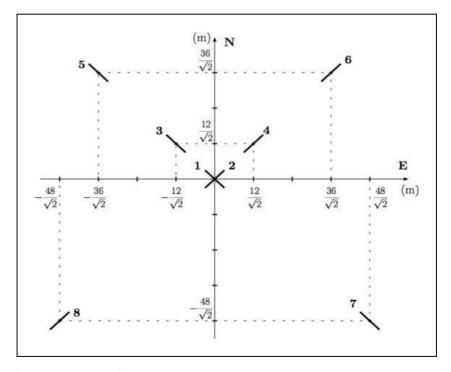

| Fig. 45. Arreglo de 8 antenas dipolo del receptor de radar VIPIR [17]       | 85  |

| Fig. 46. Una de las ocho antenas dipolo del receptor de radar VIPIR         | 86  |

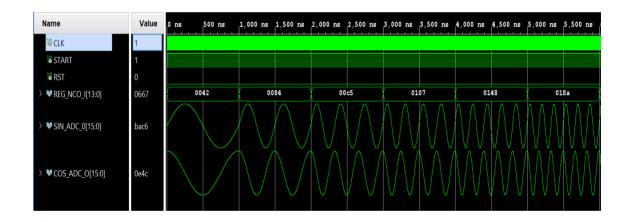

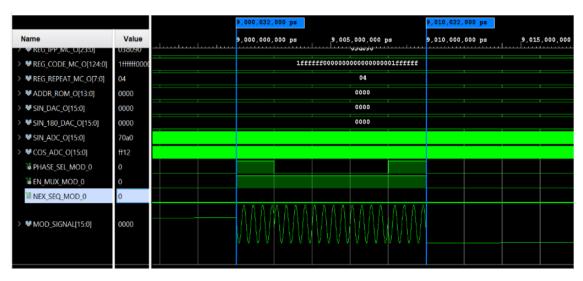

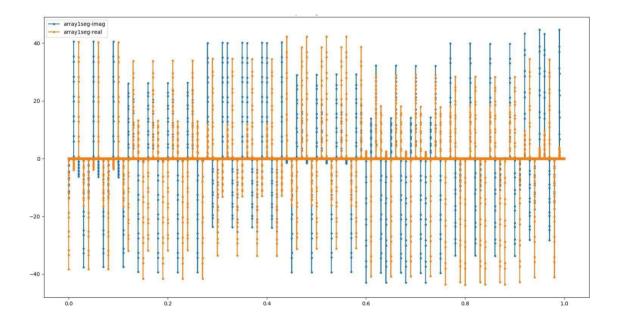

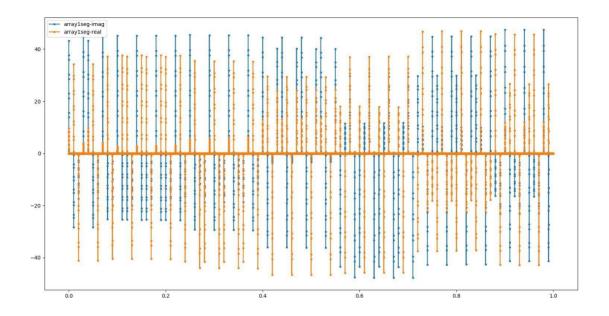

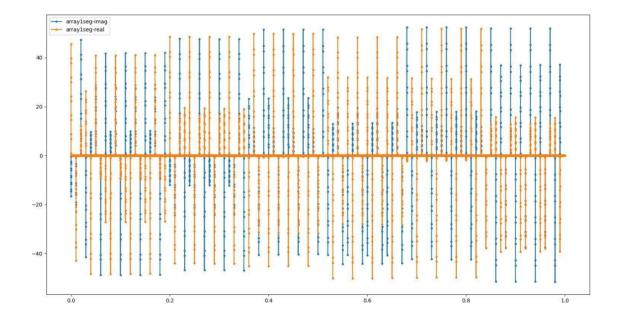

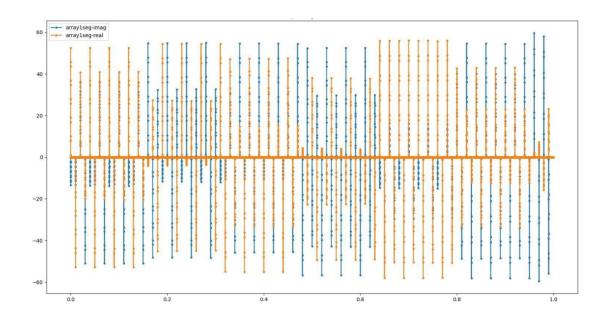

| Fig. 47. Testbench del numerically controlled controller (NCO)              | 87  |

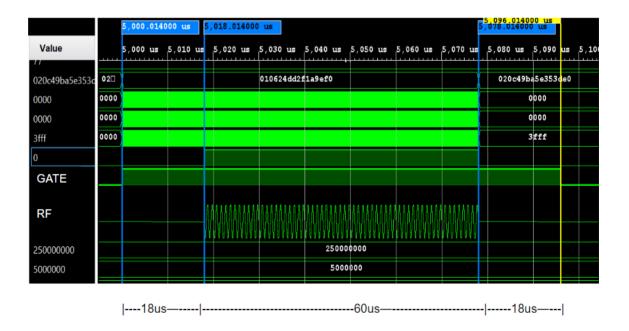

| Fig. 48. Testbench para verificación del período entre pulsos emitidos (IPP) 88                |

|------------------------------------------------------------------------------------------------|

| Fig. 49. Testbench para verificación del ancho de pulso emitido88                              |

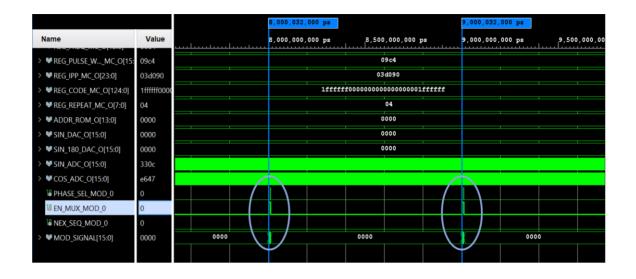

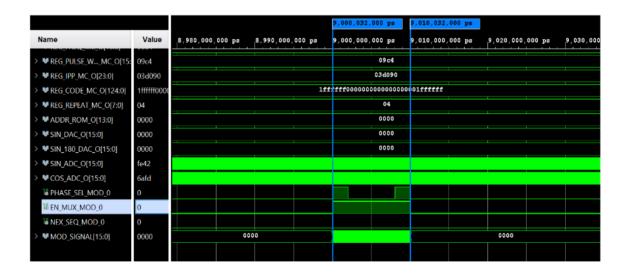

| Fig. 50. Testbench para verificación del ancho de pulso BPSK emitido89                         |

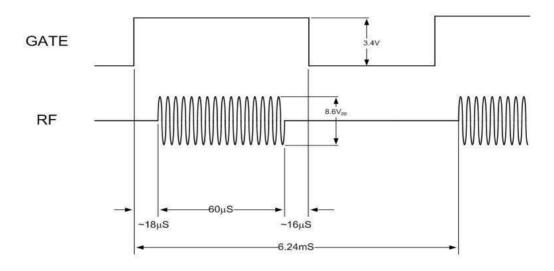

| Fig. 51. Descripción gráfica de las duraciones de tiempo y amplitudes de las                   |

| señales RF y GATE                                                                              |

| Fig. 52. Testbench de la duración de las señales RF y GATE90                                   |

| Fig. 53. Tarjeta electrónica Implementada y montada en la placa Red Pitaya Signal Lab 250-1292 |

| Fig. 54. Parte posterior del rack del generador de señales de                                  |

| radiofrecuencia para operar transmisor de radar ionosonda93                                    |

| Fig. 55. Parte frontal del rack del generador de señales de radiofrecuencia                    |

| para operar transmisor de radar ionosonda93                                                    |

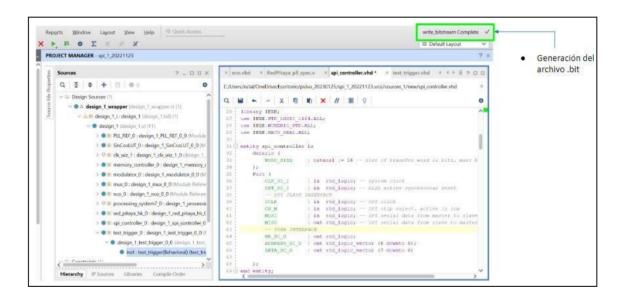

| Fig. 56. Generación del archivo Bitstream .bit en el software Vivado 2019.1 94                 |

| Fig. 57. Cargar el archivo Bitstream en la Red Pitaya Signal Lab 250-1295                      |

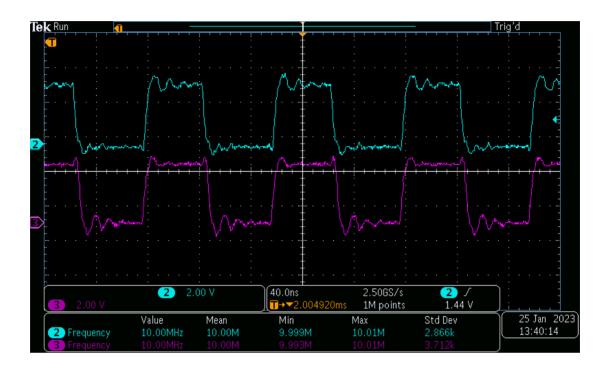

| Fig. 58. Sincronismo de la señal senoidal de clock de GPS convertida a                         |

| señal cuadrada (Lila) y clock generado por generador de señales de                             |

| radiofrecuencia (Jade)96                                                                       |

| Fig. 59. Señal de clock generada por el sistema con un jitter de 500 ps97                      |

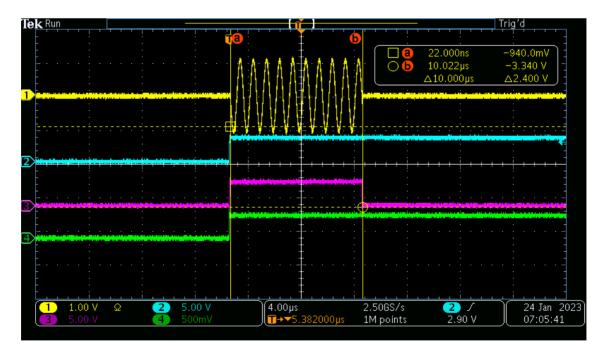

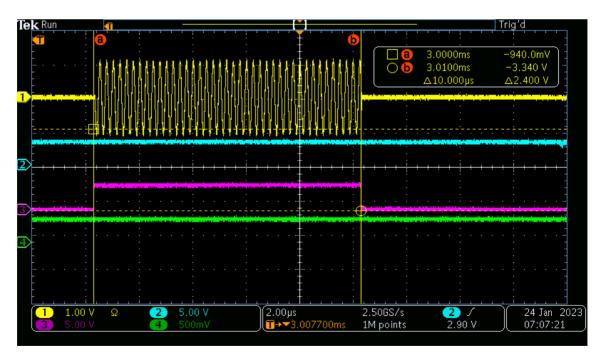

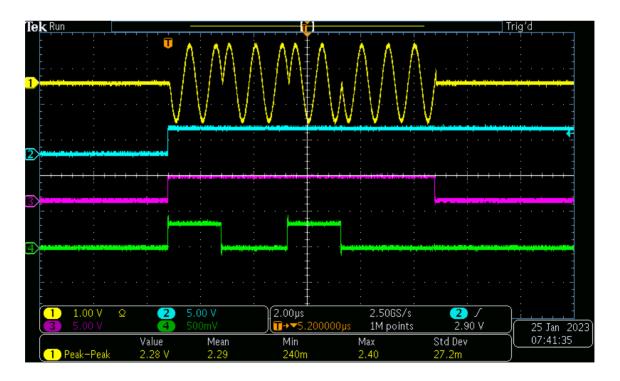

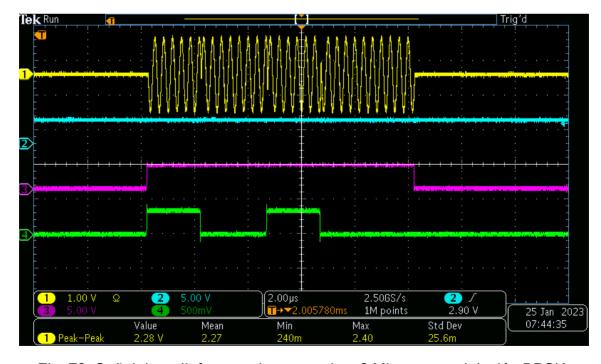

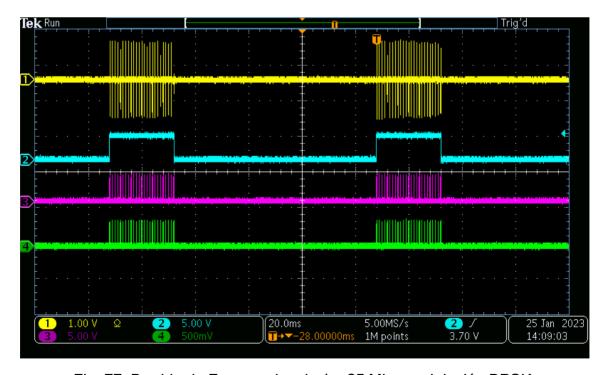

| Fig. 60. Señal de radiofrecuencia generada a 1 Mhz con modulación OOK<br>98                    |

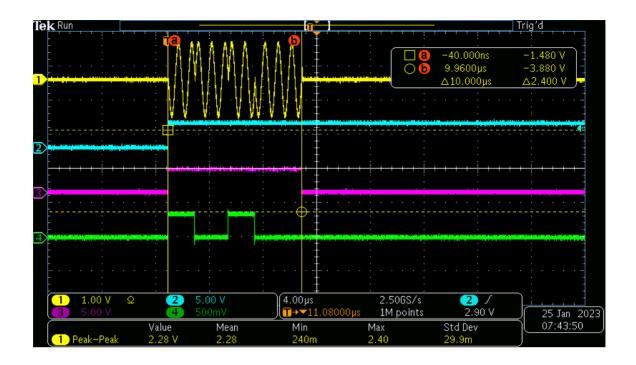

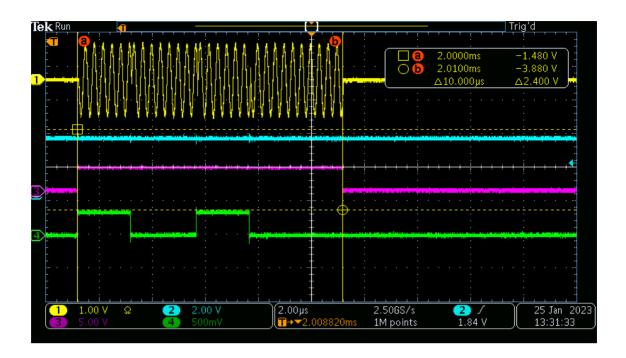

| Fig. 61. Señal de radiofrecuencia generada a 1 Mhz con modulación OOK y                        |

| ancho de pulso a 10 us medido con curso del osciloscopio98                                     |

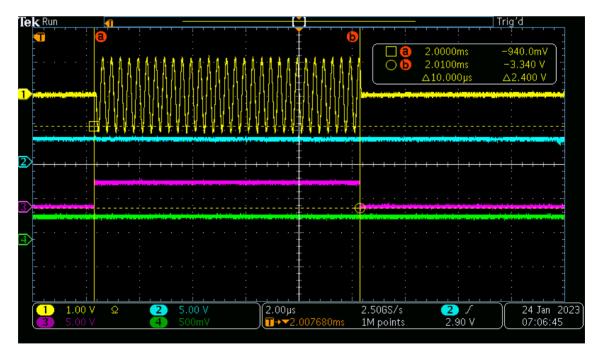

| Fig. 62. Señal de radiofrecuencia generada a 2 Mhz con modulación OOK 99                       |

| Fig. 63. Señal de radiofrecuencia generada a 2 Mhz con modulación OOK y                        |

| ancho de pulso a 10 us medido con curso del osciloscopio99                                     |

| Fig. 64. Señal de radiofrecuencia generada a 3 Mhz con modulación OOK 100                      |

| Fuente: Elaboración propia100                                                 |

|-------------------------------------------------------------------------------|

| Fig. 65. Señal de radiofrecuencia generada a 3 Mhz con modulación OOK y       |

| ancho de pulso a 10 us medido con curso del osciloscopio100                   |

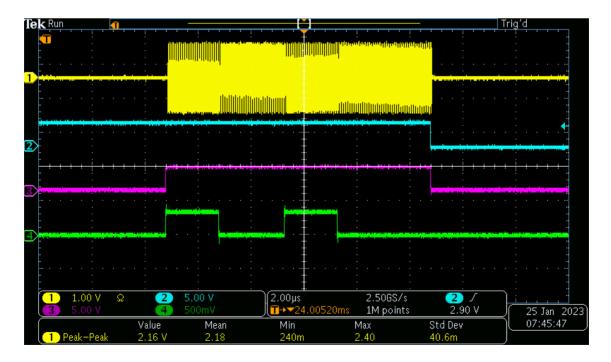

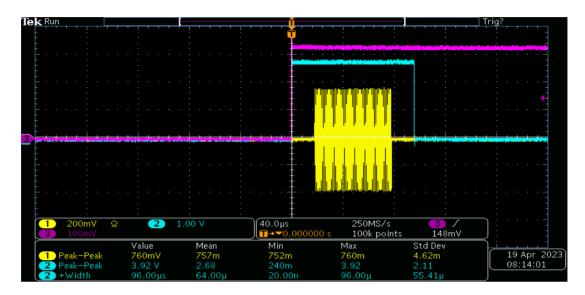

| Fig. 66. Señal de radiofrecuencia generada a 25 Mhz con modulación OOK 101    |

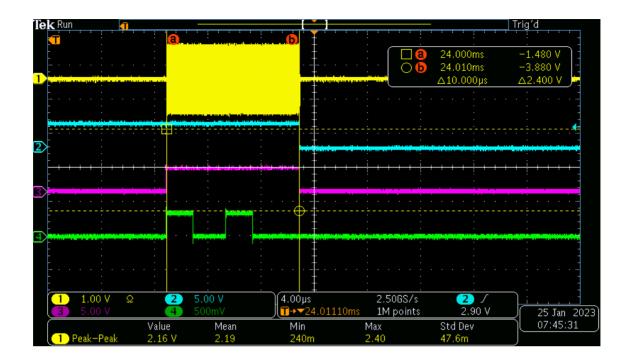

| Fig. 67. Señal de radiofrecuencia generada a 25 Mhz con modulación OOK        |

| y ancho de pulso a 10 us medido con curso del osciloscopio101                 |

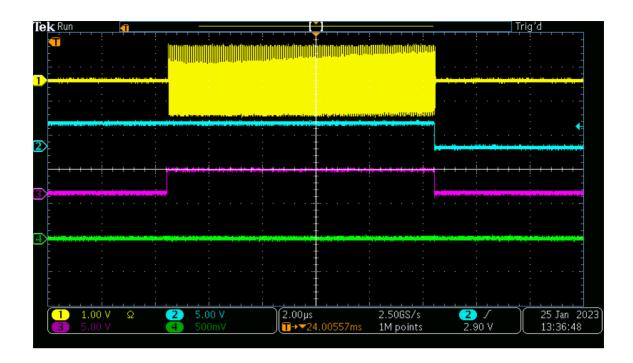

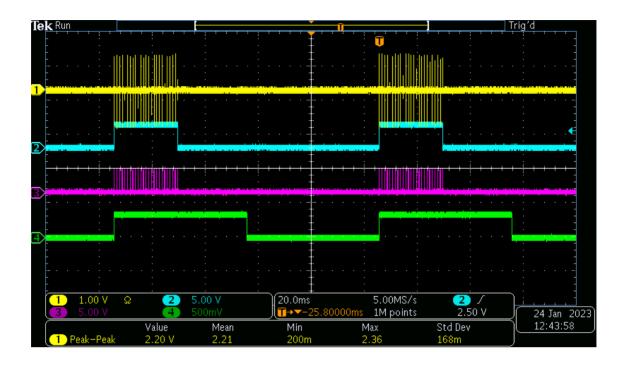

| Fig. 68. Barrido de frecuencias de 1 a 25 Mhz modulación OOK102               |

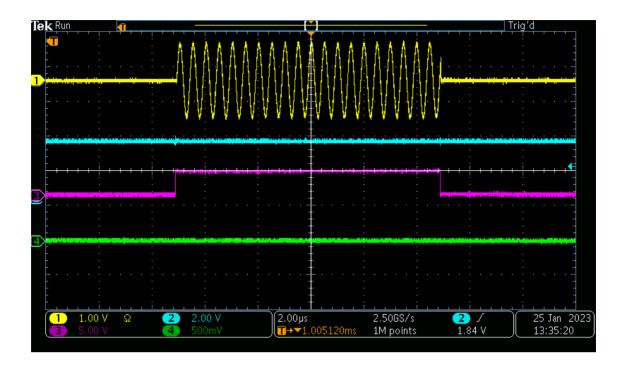

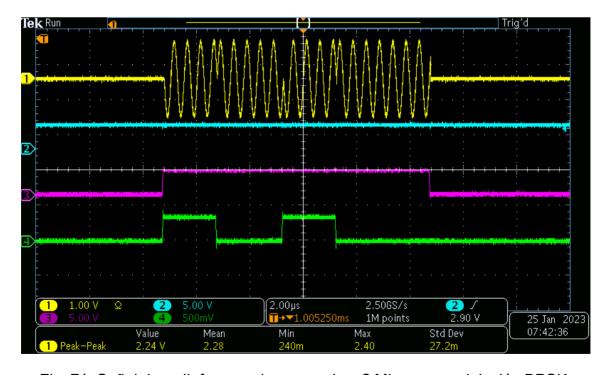

| Fig. 69. Señal de radiofrecuencia generada a 1 Mhz con modulación BPSK<br>102 |

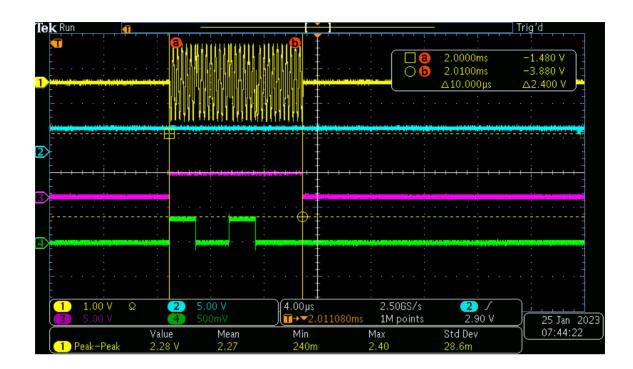

| Fig. 70. Señal de radiofrecuencia generada a 1 Mhz con modulación BPSK        |

| y ancho de pulso a 10 us medido con curso del osciloscopio103                 |

| Fig. 71. Señal de radiofrecuencia generada a 2 Mhz con modulación BPSK<br>103 |

| Fig. 72. Señal de radiofrecuencia generada a 2 Mhz con modulación BPSK        |

| y ancho de pulso a 10 us medido con curso del osciloscopio104                 |

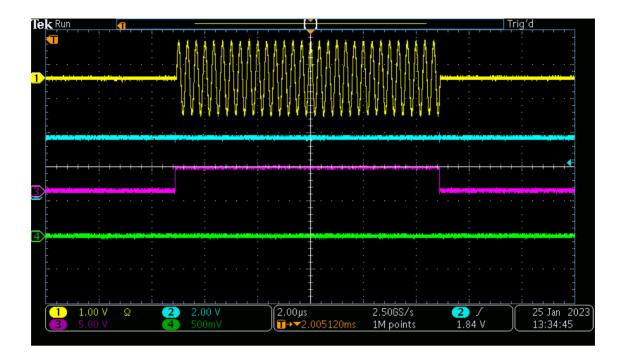

| Fig. 73. Señal de radiofrecuencia generada a 3 Mhz con modulación BPSK<br>104 |

| Fig. 74. Señal de radiofrecuencia generada a 3 Mhz con modulación BPSK        |

| y ancho de pulso a 10 us medido con curso del osciloscopio105                 |

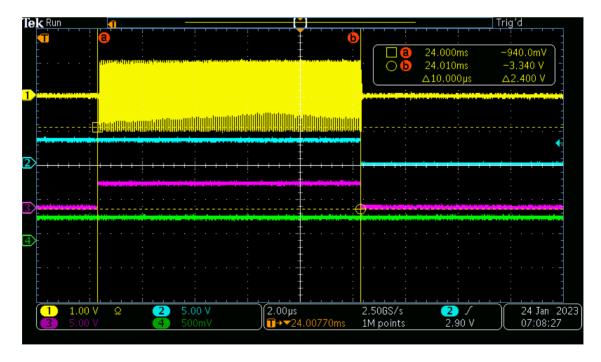

| Fig. 75. Señal de radiofrecuencia generada a 25 Mhz con modulación            |

| BPSK105                                                                       |

| Fig. 76. Señal de radiofrecuencia generada a 25 Mhz con modulación BPSK       |

| y ancho de pulso a 10 us medido con curso del osciloscopio106                 |

| Fig. 77. Barrido de Frecuencias de 1 a 25 Mhz modulación BPSK106              |

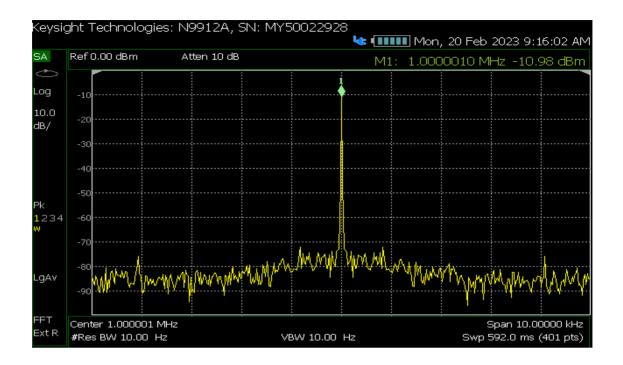

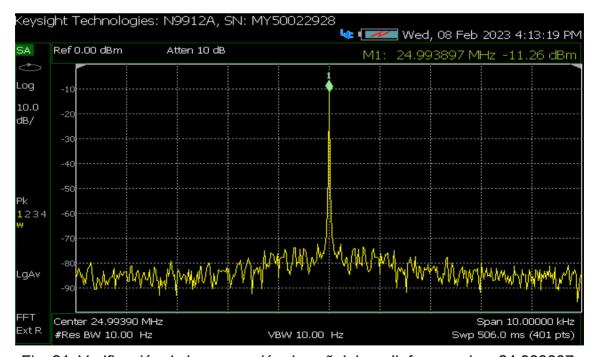

| Fig. 78. Verificación de la generación de señal de radiofrecuencia a          |

| 1.0000010 Mhz108                                                              |

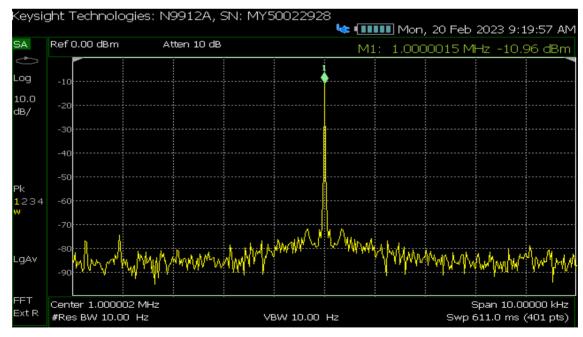

| Fig. 79. Verificación de la generación de señal de radiofrecuencia a          |

| 1.0000015 Mhz108                                                              |

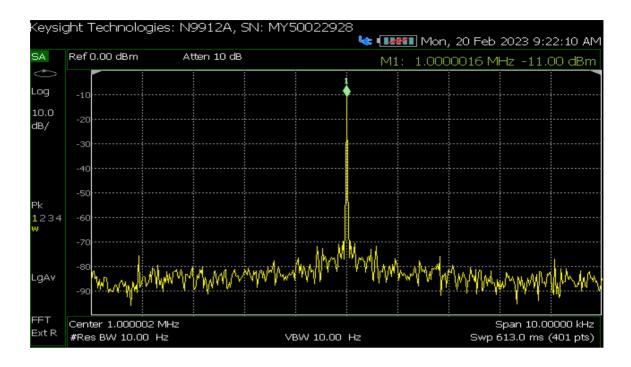

| Fig. 80. Verificación de la generación de señal de radiofrecuencia a          |

| 1.0000016 Mhz109                                                             |

|------------------------------------------------------------------------------|

| Fig. 81. Verificación de la generación de señal de radiofrecuencia a         |

| 24.993897 Mhz                                                                |

| Fig. 82. Señal RF atenuada a 760 mv110                                       |

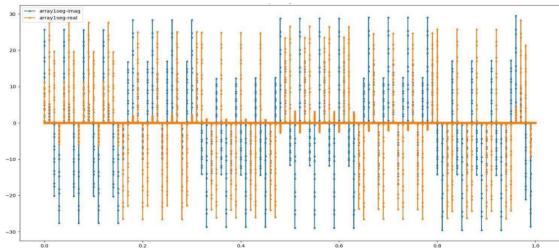

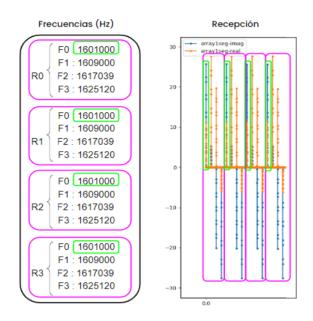

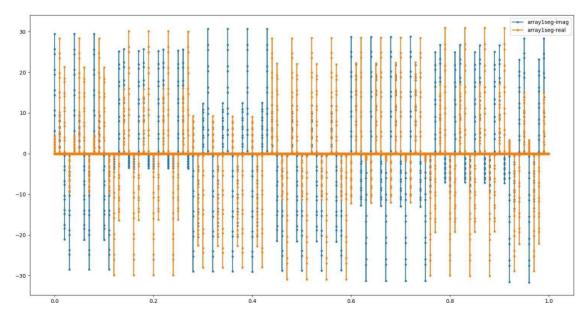

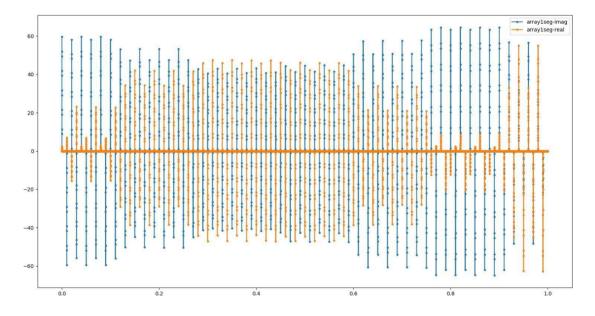

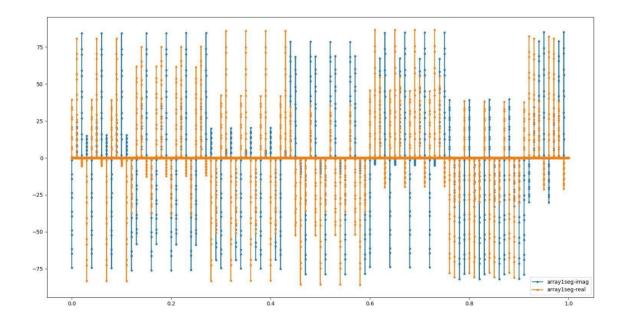

| Fig. 83. Adquisición de señales RF en el segundo 1 con el receptor IER. 110  |

| Fig. 84. Análisis del barrido de frecuencias del segundo 1                   |

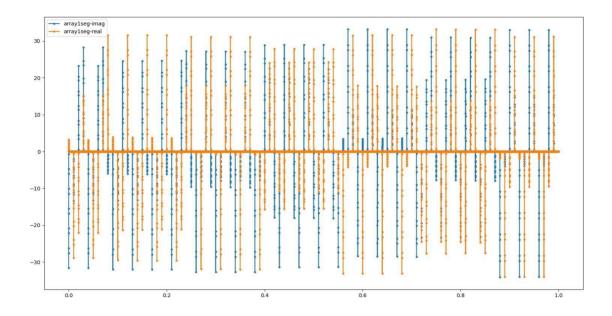

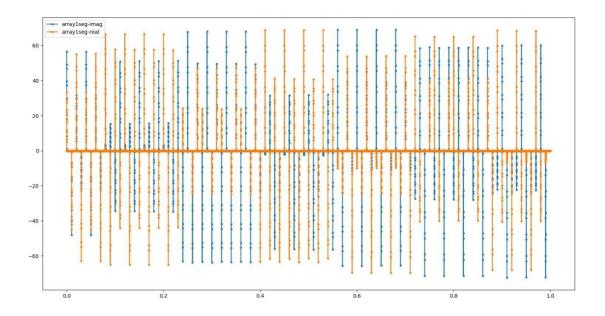

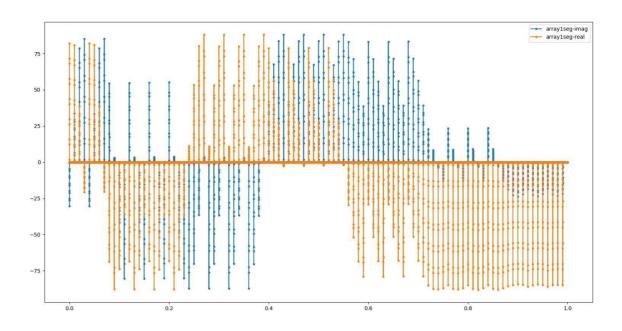

| Fig. 85. Adquisición de señales RF en el segundo 2 con el receptor IER. 111  |

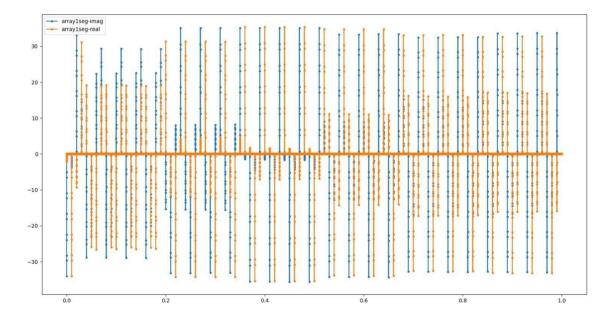

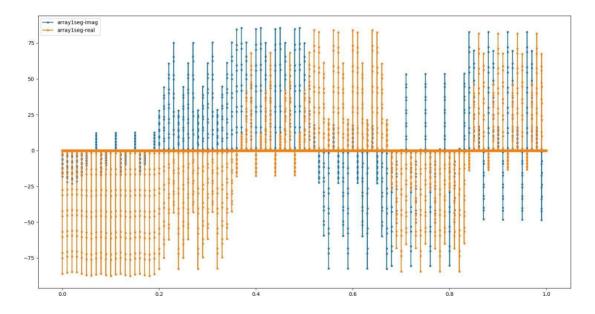

| Fig. 86. Adquisición de señales RF en el segundo 3 con el receptor IER. 112  |

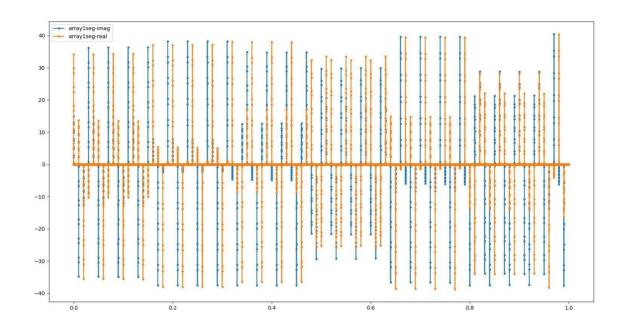

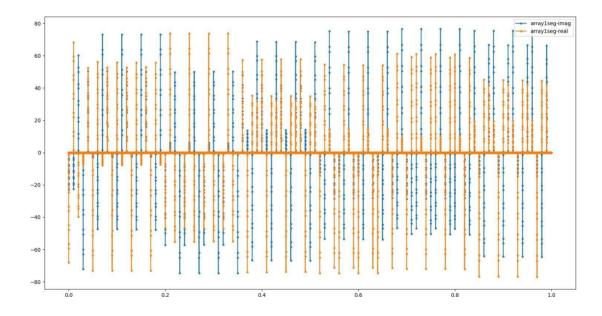

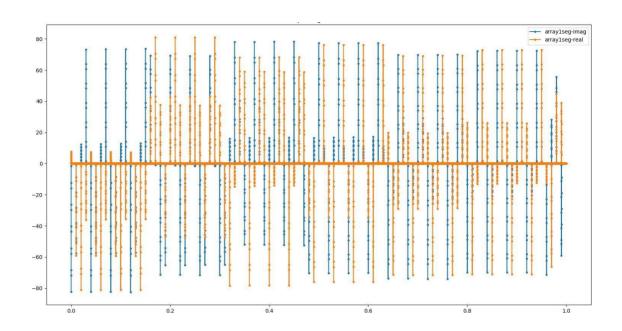

| Fig. 87. Adquisición de señales RF en el segundo 4 con el receptor IER. 112  |

| Fig. 88. Adquisición de señales RF en el segundo 5 con el receptor IER. 113  |

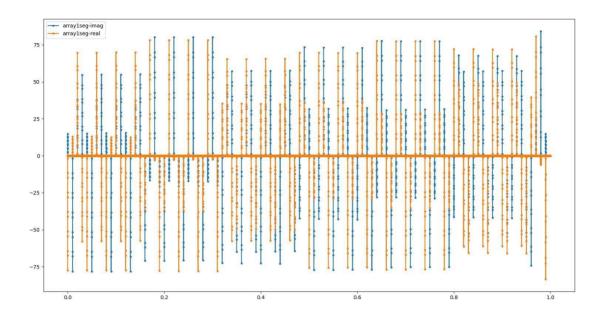

| Fig. 89 Adquisición de señales RF en el segundo 6 con el receptor IER 113    |

| Fig. 90. Adquisición de señales RF en el segundo 7 con el receptor IER. 114  |

| Fig. 91. Adquisición de señales RF en el segundo 8 con el receptor IER. 114  |

| Fig. 92. Adquisición de señales RF en el segundo 9 con el receptor IER. 115  |

| Fig. 93. Adquisición de señales RF en el segundo 10 con el receptor IER      |

| 115                                                                          |

| Fig. 94 Adquisición de señales RF en el segundo 11 con el receptor IER. 116  |

| Fig. 95. Adquisición de señales RF en el segundo 12 con el receptor IER 116  |

| Fig. 96. Adquisición de señales RF en el segundo 13 con el receptor IER 117  |

| Fig. 97. Adquisición de señales RF en el segundo 14 con el receptor IER 117  |

| Fig. 98. Adquisición de señales RF en el segundo 15 con el receptor IER 118  |

| Fig. 99. Adquisición de señales RF en el segundo 16 con el receptor IER 118  |

| Fig. 100. Adquisición de señales RF en el segundo 17 con el receptor IER 119 |

| Fig. 101. Adquisición de señales RF en el segundo 18 con el receptor IE 119               | ∃R  |

|-------------------------------------------------------------------------------------------|-----|

| Fig. 102. Adquisición de señales RF en el segundo 19 con el receptor IE 120               | ĒR  |

| Fig. 103. Ionograma con datos de bola de cobre                                            | 121 |

| Fig. 104. Señal RF atenuada a 8.48V pico pico                                             | 122 |

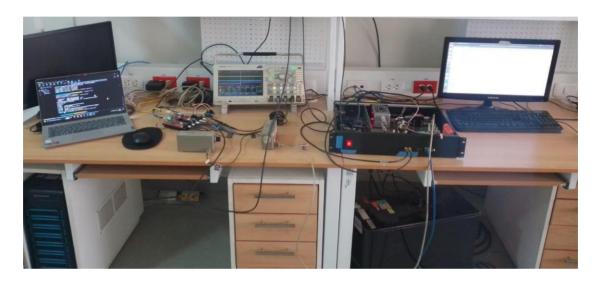

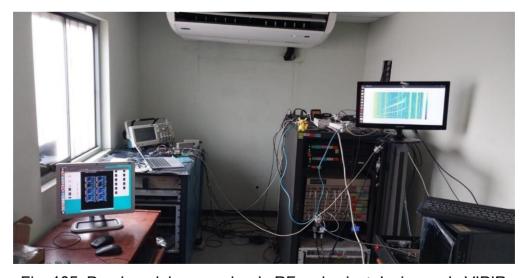

| Fig. 105. Pruebas del generador de RF en las instalaciones de VIPIR                       | 122 |

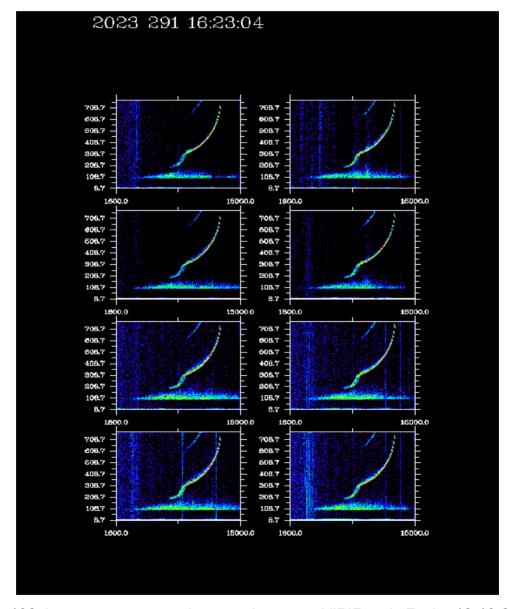

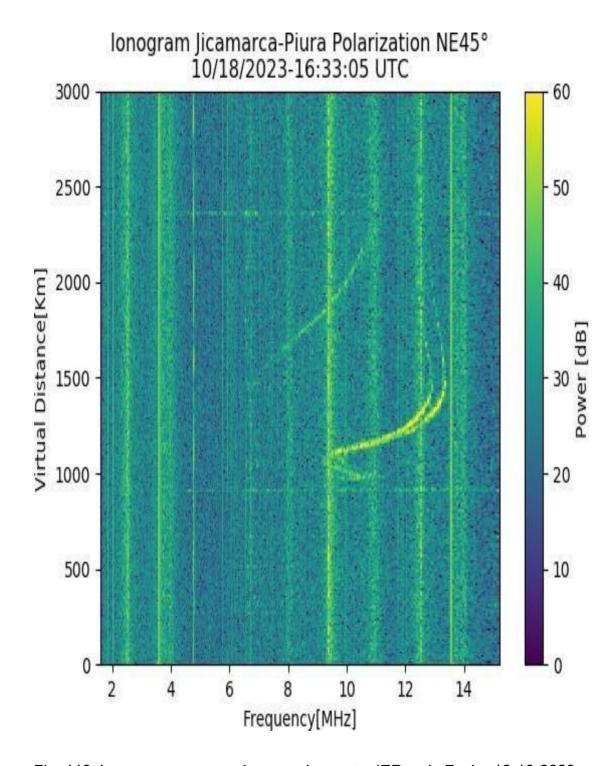

| Fig. 106. lonogramas generados con el receptor VIPIR en la Fecha:18-10-2023 hora:11:23 am | 123 |

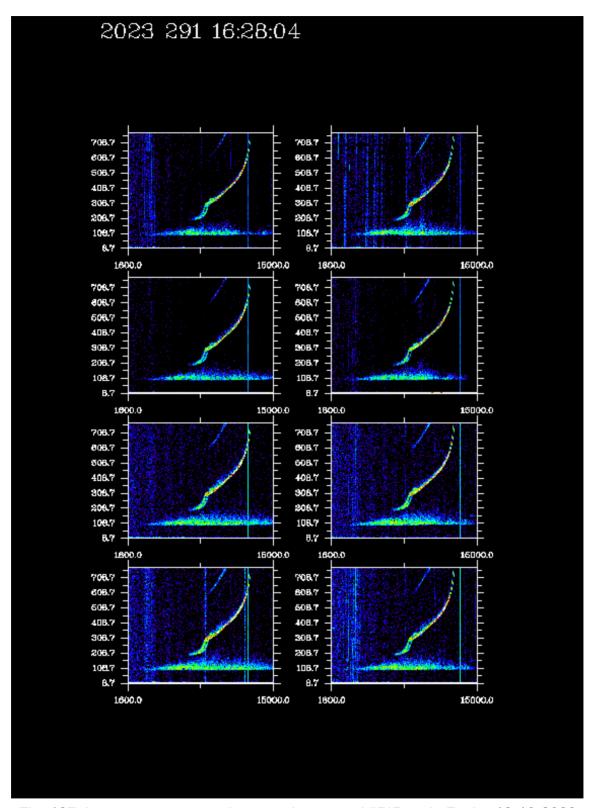

| Fig. 107. lonogramas generados con el receptor VIPIR en la                                |     |

| Fecha:18-10-2023 hora:11:28 am                                                            | 124 |

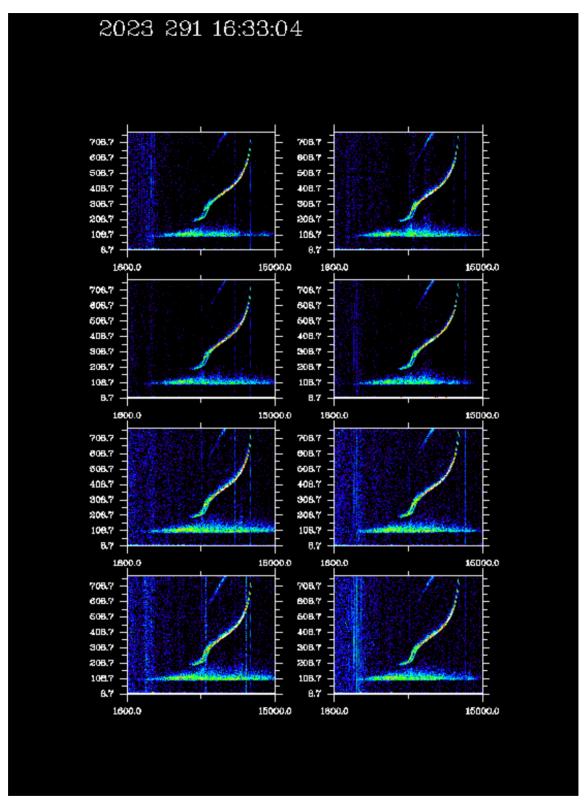

| Fig. 108. lonogramas generados con el receptor VIPIR en la Fecha:18-10-2023 hora:11:33 am | 125 |

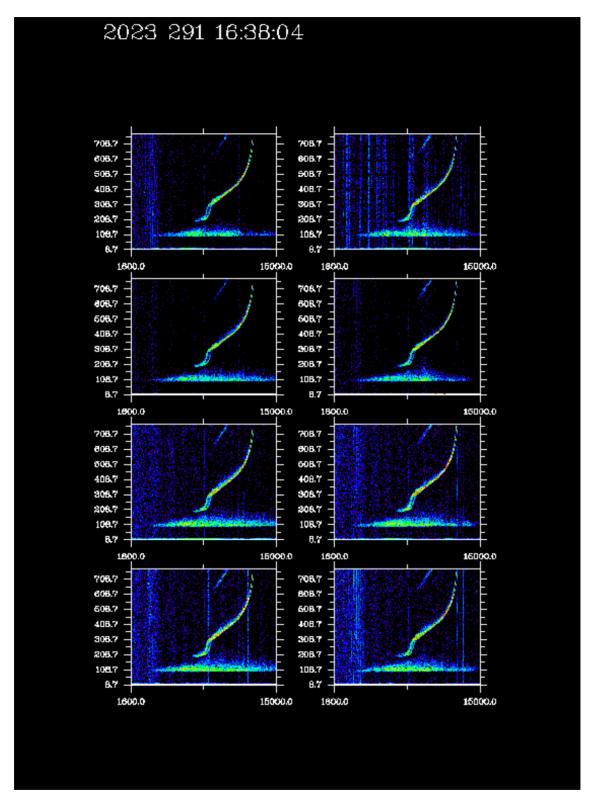

| Fig. 109. lonogramas generados con el receptor VIPIR en la Fecha:18-10-2023 hora:11:38 am | 126 |

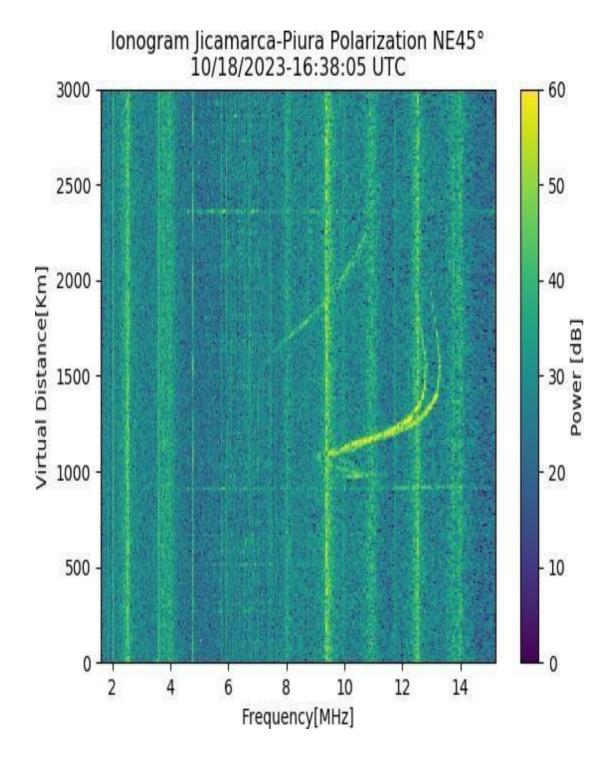

| Fig. 110. lonogramas generados con el receptor VIPIR en la Fecha:18-10-2023 hora:11:43 am | 127 |

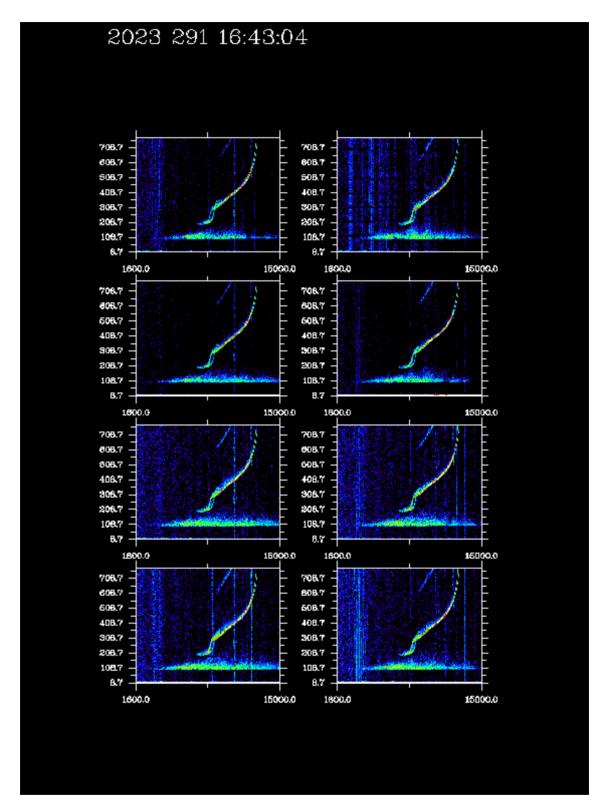

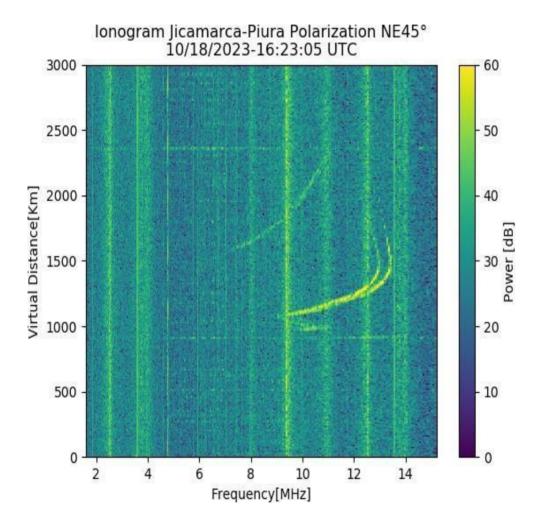

| Fig. 111. lonogramas generados con el receptor IER en la Fecha:18-10-2023 hora:11:23 am   | 128 |

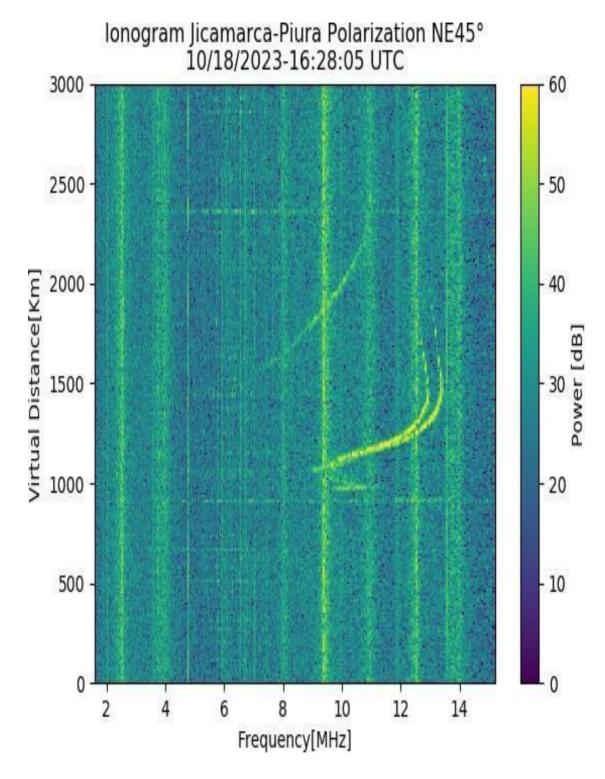

| Fig. 112. lonogramas generados con el receptor IER en la Fecha:18-10-2023 hora:11:28 am   | 129 |

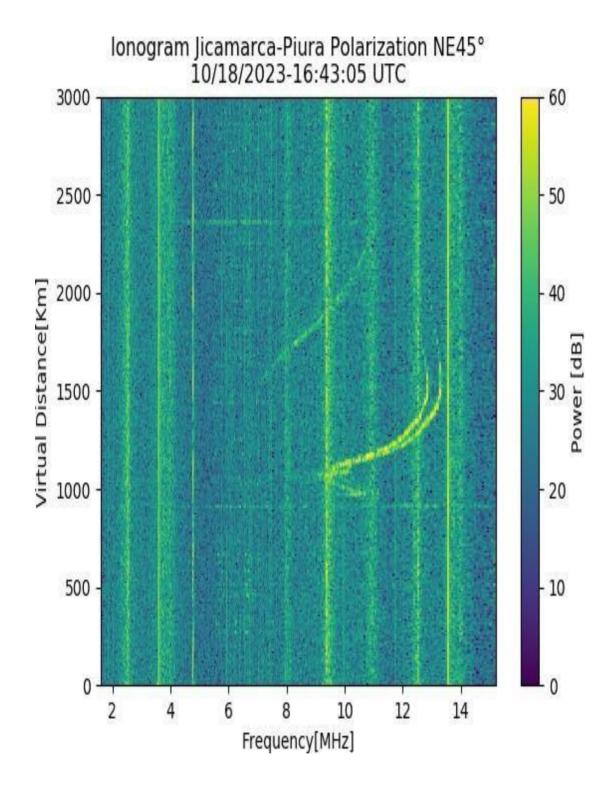

| Fig. 113. lonogramas generados con el receptor IER en la Fecha:18-10-2023 hora:11:33 am   | 130 |

| Fig. 114. lonogramas generados con el receptor IER en la Fecha:18-10-2023 hora:11:38 am   | 131 |

| Fig. 115. lonogramas generados con el receptor IER en la Fecha:18-10-2023 hora:11:43 am   | 132 |

| Fig. 116. Recursos lógicos utilizados en el generador de RF                               | 133 |

| Fig. 117. Temperatura promedio del generador de RF                                        | 134 |

| Fig. 118. Temperatura del ADC incorporado en la tarieta Red Pitava Sig                    | nal |

| Lab 250-12. | 13 | 3  | 4 |

|-------------|----|----|---|

| Lab 250-12  | Ιć | 34 | 4 |

### **ÍNDICE DE TABLAS**

| Tabla 1. Mapa de registros del generador de señales de radiofrecuencia | . 44 |

|------------------------------------------------------------------------|------|

| Tabla 2. Matriz de operacionalización                                  | 55   |

| Tabla 3. Ejemplo de repeticiones de frecuencias                        | 59   |

| Tabla 4. Tabla de mapa de registros para el controlador SPI            | 61   |

| Tabla 5. Lista de componentes electrónicos para el shield              | 71   |

#### RESUMEN

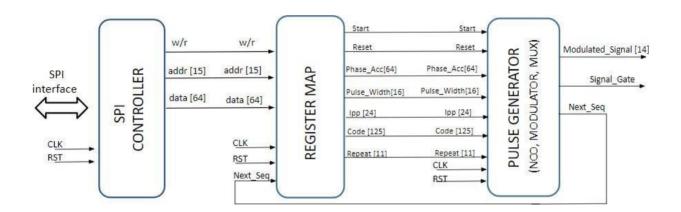

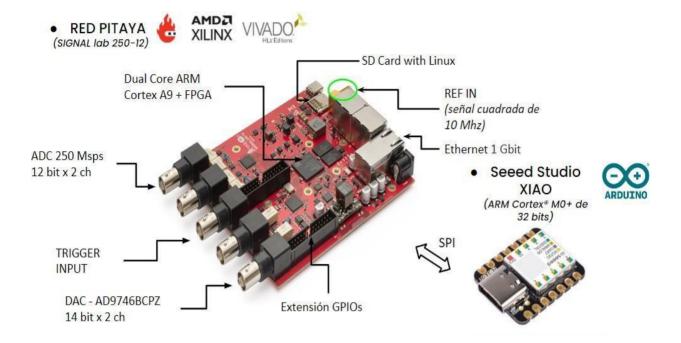

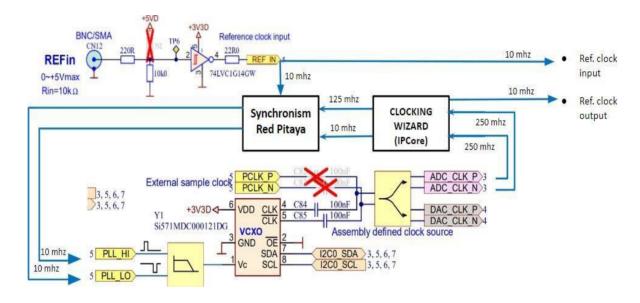

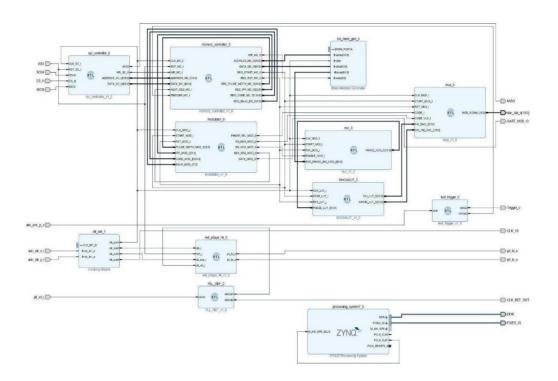

El presente trabajo de tesis tiene como objetivo principal el diseño e implementación de un generador de señales de radiofrecuencia para transmisor de radar ionosonda que está basado en el SDR Red Pitaya Signal Lab 250-12 que comprende de un FPGA SoC Zynq 7020 y puede transmitir señales moduladas con un barrido de frecuencias desde 1 MHz hasta 25 MHz. Para el diseño se utiliza el entorno de desarrollo Vivado de Xilinx-AMD. La síntesis del hardware se basa en el lenguaje VHDL y el estilo de descripción comportamental para los módulos controlador SPI, mapa de registros, oscilador controlado numéricamente (NCO), modulador BPSK y OOK, multiplexor y un módulo de sincronismo con entrada de clock de referencia de GPS de 10Mhz y trigger para el inicio de envío de las señales. Luego se agrega el Ip Core Clocking Wizard que nos permite elevar la frecuencia interna de clock del FPGA a 250 MHz.

Los módulos mencionados e Ip Cores se integran utilizando el estilo de descripción estructural con la herramienta Create Design Block en el software Vivado. Finalmente se realizaron simulaciones con banco de pruebas (test bench), pruebas de funcionamiento en el laboratorio de IDI y en la estación del radar ionosonda "Vertical Incidence Pulsed Ionospheric Radar" (VIPIR).

Palabras claves: ionosonda, Red Pitaya, SDR, sondeo ionosférico.

#### **ABSTRACT**

The main objective of this thesis work is the design and implementation of a radiofrequency signal generator for an ionosonde radar transmitter that is based on the Red Pitaya Signal Lab 250-12 SDR that comprises a Zynq 7020 SoC FPGA and can transmit signals. modulated with a frequency sweep from 1 MHz to 25 MHz.

The Xilinx-AMD Vivado development environment is used for the design. The hardware synthesis is based on the VHDL language and behavioral description style for the SPI controller modules, register map, numerically controlled oscillator (NCO), BPSK and OOK modulator, multiplexer, and a synchronization module with reference clock input 10Mhz GPS and trigger to start sending signals. Then the IP Core Clocking Wizard is added that allows us to raise the internal clock frequency of the FPGA to 250 MHz.

The mentioned modules and IP Cores are integrated using the structural description style with the Create Design Block tool in the Vivado software. Finally, simulations were carried out with a test bench, and functional tests in the IDI laboratory and at the "Vertical Incidence Pulsed Ionospheric Radar" (VIPIR) ionosonde radar station.

Keywords: ionosonde, Pitaya Network, SDR, ionospheric survey.

#### INTRODUCCIÓN

Con los avances tecnológicos actuales el estudio de la aeronomía es de suma importancia para los sistemas de posicionamiento global basados en satélites (GNSS) y las aplicaciones derivadas de ellos, por ejemplo, la radionavegación terrestre, marítima y aérea.

En diversas partes del mundo, se han realizado numerosos estudios con el fin de analizar el comportamiento de la propagación de señales de radio en la ionosférica, dichos estudios arrojaron como resultado la presencia de errores en la recepción de datos, derivados de los retardos en la propagación [1].

Una ionosonda es un radar de HF que envía un barrido de pulsos electromagnéticos entre 1 a 25mhz hacia la ionosfera las cuales son reflejadas y recibidas posteriormente para procesar el eco. Los ionogramas son la relación frecuencia de sondeo versus altura virtual de reflexión y nos dan una idea aproximada de la densidad electrónica de la ionósfera [2]. Por lo que, controlar la operación de un transmisor de radar ionosférico permitiría estudiar las capas altas de la atmósfera además de cumplir un rol importante en la obtención de densidades de electrones y corregir errores en los sistemas GNSS.

En el presente proyecto de investigación se busca diseñar e implementar un generador de señales de radiofrecuencia basado en FPGA SoC para operar un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca.

#### I.PLANTEAMIENTO DEL PROBLEMA

#### 1.1. Descripción de la realidad problemática

En el territorio peruano la propagación de radiofrecuencias se ve afectada por su interacción con la ionósfera sin poderse corregir, dando como resultado diferentes fenómenos que alteran su comportamiento de manera impredecible. El Radio Observatorio de Jicamarca (ROJ) que es sede científica del Instituto Geofísico del Perú (IGP) realiza estudios de aeronomía con la finalidad de comprender las capas altas de la atmósfera específicamente la ionósfera, en las cuales los procesos de ionización y recombinación son importantes.

Las ionosondas son instrumentos científicos que nos permiten obtener los parámetros ionosféricos y sus efectos en las señales del sistema global de navegación por satélite (GNSS).

Existen ionosondas como Digisonde que son instrumentos reconocidos mundialmente. Sin embargo, son muy costosos el importarlos y darle el mantenimiento respectivo. Y en orden de exitosamente realizar estudios de aeronomía, un generador de señales de radiofrecuencia para operar un transmisor de radar ionosonda es requerido.

En el presente proyecto de investigación se propondrá un diseño de un generador de señales de radiofrecuencia basado en Red Pitaya que comprende de un FPGA SoC para operar un transmisor de radar ionosonda, dicho generador transmitirá una señal modulada con un sweep de frecuencias desde 1 MHz hasta 25 MHz el cual permite el estudio de la ionósfera en el Radio Observatorio de Jicamarca.

#### 1.2. Formulación del problema

#### 1.2.1. Problema general

❖ Problema general: ¿Es posible diseñar e implementar un generador de señales de radiofrecuencia basado en FPGA SoC para operar un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca?

#### 1.2.2. Problemas específicos

- ❖ Problema específico 1: ¿Es posible diseñar e implementar un generador de señales de radiofrecuencia basado en FPGA SoC para sincronizar la señal de GPS en un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca?

- ❖ Problema específico 2: ¿Es posible diseñar e implementar un generador de señales de radiofrecuencia basado en FPGA SoC para emitir un barrido de frecuencias en un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca?

- Problema específico 3: ¿Es posible diseñar e implementar un circuito modulador de señales de radiofrecuencia basado en FPGA SoC?

#### 1.3. Objetivos

#### 1.3.1. Objetivos generales

Objetivo general: Diseñar e implementar un generador de señales de radiofrecuencia basado en FPGA SoC para operar un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca.

#### 1.3.2. Objetivos específicos

- Objetivo específico 1: Diseñar e implementar un generador de señales de radiofrecuencia basado en FPGA SoC para sincronizar la señal de GPS en un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca.

- Objetivo específico 2: Diseñar e implementar un generador de señales de radiofrecuencia basado en FPGA SoC para emitir un barrido de frecuencias en un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca.

- Objetivo específico 3: Diseñar e implementar un circuito modulador de señales de radiofrecuencia basado en FPGA SoC.

#### 1.4. Justificación

#### 1.4.1. Justificación Teórica

La justificación teórica tiene como propósito generar reflexión y debate académico sobre el conocimiento existente, contrastar resultados o hacer epistemología del conocimiento existente [5].

De lo expuesto del autor, el presente trabajo de investigación tiene una justificación teórica ya que se estudiará la teoría de radares ionosféricos para el nuevo diseño de generador de señales para radar ionosonda que aporta con el conocimiento y la utilización de la misma en otros trabajos de investigación.

#### 1.4.2. Justificación Práctica

Se tiene justificación práctica cuando el desarrollo de un proyecto ayuda a resolver un problema o, por lo menos, propone estrategias que al aplicarse contribuirían a resolverlo [5].

De lo expuesto por el autor, el presente trabajo de investigación tiene una justificación práctica puesto que el generador de señales de radiofrecuencia permitirá operar el transmisor de radar ionosonda para el estudio de la aeronomía.

#### 1.4.3. Justificación Metodológica

La justificación metodológica se refiere cuando un proyecto propone un nuevo método o una nueva estrategia para generar conocimiento válido y confiable [5].

De lo expuesto por el autor, el presente trabajo de investigación tiene una justificación metodológica ya que en él se propone un esquema metodológico innovador que tiene como finalidad un nuevo diseño de generador de señales de radiofrecuencia para el transmisor de radar ionosonda que será puesto en evaluación en todo el periodo de implementación del mismo.

#### 1.4.4. Justificación Social

Se refiere a cuál es su trascendencia para la sociedad, quiénes o en qué modo se beneficiarán con los resultados de la investigación, en conclusión, ¿qué alcance o proyección social tiene? [6].

De lo expuesto por el autor, el presente trabajo de investigación tiene una justificación social puesto que al operar el transmisor de radar ionosonda se obtendrá información de los fenómenos ionosféricos que beneficiará a la sociedad.

#### 1.5. Limitaciones de la investigación

#### 1.5.1. Limitación teórica

El presente trabajo de investigación presenta una limitación teórica dado que existen pocas referencias bibliográficas o escasa información sobre el diseño de generadores de señales de radiofrecuencia para radares ionosféricos.

#### II. MARCO TEÓRICO

#### 2.1. Antecedentes: Internacional y nacionales

#### 2.1.1. Antecedentes internacionales

❖ En el artículo científico titulado: "Implementación de una lonosonda electrónica para la supervisión de la ionosfera desde la Tierra vía una columna proyectada a través de USRP" [2] publicado MULTIDISCIPLINARY DIGITAL PUBLISHING INSTITUTE (MDPI), se tuvo como objetivo plantear una propuesta de monitoreo del contenido total de electrones de la ionosfera desde el punto de vista instrumental. Se utilizó la metodología de diseño de instrumentación científica, se diseña un radar para sondeo ionosférico basado en tecnología USRP con la finalidad de conocer el comportamiento o respuesta de cada modelo en una zona de alta actividad ionosférica, dentro de la franja de anomalía ecuatorial (diseño experimental, enfoque cuantitativo y nivel descriptivo). Se llegó a la conclusión de que la implementación de una ionosonda usando tecnología USRP cumple con las características deseadas y el post-procesamiento es capaz de imprimir las alturas de la ionosfera para el rango diseñado.

De este trabajo de investigación se puede destacar cómo implementaron un transmisor de radar ionosonda para generar la forma de los pulsos de radar y el procesamiento de la información de los ecos provenientes de la ionosfera.

En el artículo científico titulado: "Diseño en FPGA de una ionosonda generación" [3] indexado en la revista digital de las tecnologías de la información y las comunicaciones, se tuvo como objetivo el diseño de un radar de sondeo vertical de la ionosfera, para ello se utilizó la metodología de la técnica de modulación por código binario de fase y compresión de pulsos (diseño experimental, enfoque cuantitativo y nivel

descriptivo). Llegando a la conclusión de que las técnicas actuales de compresión de pulsos y modulación por código binario de fase aumenta la relación señal a ruido además de proporcionar una ganancia de procesamiento lo cual se comprueba mediante simulaciones realizadas en los softwares Simulink y Quartus. Finalmente, el autor recomienda culminar la simulación de la integración coherente debido a que la computadora no cumplía con los requerimientos para tal simulación y los resultados preliminares obtenidos de las simulaciones constituyen un punto de partida para la futura implementación física del diseño de una ionosonda en el Instituto de Geofísica y Astronomía en Cuba.

Del artículo desarrollado por el autor, se aprecia cómo utilizan el software Quartus para el diseño, simulación y síntesis de hardware del transmisor de radar ionosonda basado en FPGA.

#### 2.1.2. Antecedentes nacionales

Proyecto de investigación titulado: "Implementación de sistema de radar ionosonda en RED PITAYA" [3] publicado en el repositorio de prácticas preprofesionales del Radio Observatorio de Jicamarca (ROJ), tuvo como objetivo el diseño de un sistema de radar ionosonda basado en red pitaya que transmite una onda modulada con un sweep de frecuencias desde 1 MHz hasta 25 MHz, teniendo la posibilidad de modular la señal portadora durante cada step del sweep, para ello se utilizó la metodología de diseño electrónico por bloques del radar ionosonda enfocado a pruebas de laboratorio, que tiene como primer paso la recolección de los requisitos funcionales, luego levantar los diagramas esquemáticos y posteriormente proceder con simulaciones por bloque (diseño experimental, enfoque cuantitativo y nivel descriptivo).

El autor concluye que se ha logrado simular el diseño del sistema de transmisión, recepción y de interfaz entre el FPGA y el procesador en el software VIVADO. Finalmente, el autor recomienda realizar el test bench

lógico global del diseño de radar ionosonda y testear el sistema transmitiendo mediante una antena e incorporar una señal de GPS para el sincronismo del mismo.

Del trabajo de investigación desarrollado por el autor, se concluye la importancia de la recolección de los requisitos funcionales del radar ionosonda y posteriormente analizar y diseñar el sistema radar mediante descripción por bloques, además de utilizar los Ip Core brindados en el software VIVADO. Se resalta que dentro de los antecedentes nacionales solo existe dicha investigación.

#### 2.2. Bases teóricas

#### 2.2.1. Ionósfera

La ionosfera es la parte superior de atmósfera terrestre que se extiende aproximadamente desde los 50 a 1000 km, está conformada por moléculas disociadas y partículas cargadas eléctricamente, por efectos de la radiación ultravioleta y los rayos X del sol, las moléculas suspendidas en esta parte superior de la atmósfera, son calentadas y agitadas a tal punto que sufren diferentes procesos de disociación que involucran desprendimientos de electrones [2].

Las variaciones del comportamiento en la ionósfera, están directamente relacionadas con la radiación emitida desde el sol, el movimiento de la Tierra y los cambios en la actividad solar.

Esta parte de la atmósfera comprende capas denominadas D, E, F1, F2. Las capas D, E y F1 dependen de los ángulos de incidencia del sol y tienen un mayor tamaño de la densidad de ionización en verano que en invierno,

en cambio la capa F2 tiene un mayor tamaño de ionización en invierno que en verano.

Las múltiples aplicaciones de radiocomunicaciones que utilizamos actualmente dependen del comportamiento del plasma ionosférico. El término plasma se refiere a gases parcial o totalmente ionizados [18]. Debido a los diversos factores que afectan la ionosfera es de suma importancia desarrollar y poner en operación instrumentos científicos que nos ayuden a estudiar el clima espacial y modelar el comportamiento de la ionosfera.

#### 2.2.2. Radar ionosonda

Una ionosonda es un radar HF que transmite pulsos electromagnéticos en un barrido de frecuencias desde un determinado punto de la Tierra hacia la ionosfera y las señales reflejadas son recepcionadas en el mismo u otro punto de la Tierra. Los pulsos enviados a la ionosfera logran tener la máxima intensidad de reflexión cuando la frecuencia de propagación de la onda de radio es igual a la frecuencia del plasma ionosférico.

Al procesar el eco las ionosondas realizan un registro de la reflexión llamado la altura virtual vs la frecuencia que fue enviada la señal, a esta construcción de registros se les conoce como perfil ionosférico o ionogramas y en ellos se puede visualizar el comportamiento de la ionosfera.

El Centro de Investigaciones Atmosféricas de la Universidad de Massachusetts Lowell (UMLCAR) ha producido una versión de baja potencia de sus sondas Digisonde TM, la sonda portátil Digisonde TM (DPS) capaz de realizar mediciones de la ionosfera superior y proporcionar procesamiento en tiempo real y análisis para caracterizar la propagación de la señal de radio para apoyar las comunicaciones o las operaciones de vigilancia [7].

Fig. 1. Sistema digisonda DPS-4 [8].

Fig. 2. Antena transmisora delta cruzada simple del sistema DPS-4 [16].

Fig. 3. Una de las 4 antenas receptoras del sistema DPS-4 [16].

#### 2.2.3. Rango, resolución y ecuación del radar

#### a. Altura virtual (hv)

Las ionosondas tienen como principal objetivo medir la altura a la cual se refleja una frecuencia específica en alguna capa de la ionosfera. Para calcular la distancia a la cual se refleja la señal transmitida o también llamada altura virtual (hv), se emplea la siguiente ecuación 2.1 [9].

$$h_{v} = \frac{C.\Delta t}{2} \tag{2.1}$$

Donde:

$h_{_{\!\scriptscriptstyle V}}$  : representa una altura que no es la real sino la altura a la cual se

reflejaría la señal si viajara a la velocidad de la luz.

C : Velocidad de la luz.

$\Delta t$ : Tiempo de demora del eco reflejado.

b. Altura máxima

Los parámetros de los cuales depende directamente la altura máxima son la

capacidad de detección del sistema, frecuencia de repeticiones del pulso

(frp) del radar ionosonda o su inversa qué es el tiempo máximo de retardo

del pulso (trp).

Cabe mencionar que se requiere esperar un tiempo suficiente después del

pulso emitido para que sea detectado antes de que se transmita el siguiente

pulso por el radar ionosonda. Por consiguiente, la frecuencia a la cual los

pulsos pueden ser transmitidos está determinada por la mayor altura que

esta puede transmitir.

La altura máxima se representa en la siguiente ecuación 2.2:

$$H = \frac{C}{2.f.r.p} \tag{2.2}$$

Donde:

H: Altura máxima, se sustituye por la altura virtual  $h_{\nu}$  en la ecuación 2.1.

frp: frecuencia de repetición de pulsos, se sustituye por el inverso del tiempo

de demora del eco reflejado  $\Delta t$  en la ecuación 2.1.

35

#### c. Resolución

La resolución es la distancia mínima en la que la ionosonda puede detectar entre dos blancos diferentes, en este caso específico de estudio de aeronomía puede detectar diferentes capas ionosféricas.

La resolución se representa en la siguiente ecuación 2.3:

$$\Delta H = \frac{C.T}{2} = \frac{C}{2.B} \tag{2.3}$$

$\Delta H$ : Resolución, se sustituye por la altura virtual *hv* en la ecuación 2.1.

T: Representa la longitud del pulso, se sustituye por el inverso del tiempo de demora del eco reflejado  $\Delta t$  en la ecuación 2.1.

B: El ancho de banda del radar y es igual al inverso de la longitud del pulso B=1/T.

## d. Ecuación del radar

Según los principios de diseño de sistemas de radar, la ecuación del radar es la estimación del rango en función de características deseadas y se representa en la ecuación 2.4 [12].

$$P_r = \frac{P_t \cdot G_t}{4\pi \cdot R^2} \cdot \frac{\sigma}{4\pi \cdot R^2} \cdot A_e \tag{2.4}$$

Donde:

Pr: Potencia recibida.

Pt: Potencia irradiada.

Gt: Ganancia de la antena.

σ: Superficie efectiva de dispersión.

Ae: Área efectiva de la antena receptora.

R: Distancia

Teniendo en cuenta las consideraciones de la ecuación del radar y si se define el rango máximo del radar R máx., cuando la señal recibida es igual a la mínima señal detectable se obtiene la ecuación 2.5 [12].

$$R_{m\acute{a}x}^{4} = \frac{P_t \cdot G_t \cdot A_e \cdot \sigma}{(4\pi)^2 \cdot S_{m\acute{n}}} \tag{2.5}$$

Se concluye que para obtener una alta resolución se requiere de pulsos de corta duración y para detectar blancos distantes es necesario una gran potencia pico de pulso Pt además de una larga duración de pulso t, o una pequeña frp.

# 2.2.4. lonograma

Los ionogramas son mediciones de trazos correspondientes al barrido de señales de alta frecuencia reflejados, los cuales son generados por una ionosonda. Debido a que los pulsos de radio viajan más lento dentro de la ionósfera que en espacio libre, la altura aparente o "virtual" es medida en vez de la altura real.

Para frecuencias cercanas al máximo nivel de frecuencia en la capa correspondiente, la altura virtual tiende al infinito debido a que el pulso debe viajar una distancia finita a una velocidad cero. Las frecuencias en las que se produce dicho fenómeno se denominan frecuencias críticas [1].

Con los ionogramas se pueden obtener los siguientes parámetros de las señales reflejadas: frecuencia, alcance (o altura para mediciones de incidencia vertical), amplitud, fase, desplazamiento y propagación Doppler, ángulo de llegada y polarización de onda.

Fig. 4. lonograma escalado automáticamente con software ARTIST4 [8].

## 2.2.5. Matrices de puertas programables por campo FPGA

Una FPGA es un tipo de dispositivo electrónico formado por bloques funcionales unidos a través de un array de conexiones programables, permitiéndonos describir un circuito digital a partir de un lenguaje descriptivo que puede ser el VHDL o Verilog. Internamente se componen principalmente de puertas lógicas, biestables, memorias, multiplexores, puertos de entrada y salida, entre otros.

En comparación con un procesador, este tiene una estructura fija y se modifica su comportamiento a través del programa escrito, ejecutado de forma secuencial. En cambio, en una FPGA se varía la estructura interna, constituyendo un circuito electrónico, lo que permite que tanto la eficiencia como la velocidad debido a que la FPGA puede trabajar en paralelismo.

## 2.2.6. Red Pitaya SIGNAL lab 250-12

SIGNAL lab 250-12 es el producto de Red Pitaya más sofisticado, creado para aplicaciones industriales e investigación más exigentes, donde la robustez y el rendimiento al sintetizar hardware dentro de estos dispositivos. Esta tarjeta de evaluación está equipada con PoE (alimentación a través de Ethernet), lo que brinda la posibilidad de alimentar y comunicarse con SIGNAL lab utilizando un solo cable Ethernet, internamente comprende de una FPGA Xilinx Zynq 7020, un ARM Cortex-A9 C de doble núcleo, Frecuencia de muestreo 250MSPS, resolución de DAC de 14 bits y resolución de ADC de 12 bits.

Fig. 5. Tarjeta de evaluación Red Pitaya SIGNAL lab 250-12 [10].

## 2.2.7. Lenguaje de descripción de hardware (VHDL)

Es un lenguaje de descripción y modelado diseñado para describir la funcionalidad y la organización de sistemas hardware digitales. El VHDL es un lenguaje con una sintaxis amplia y a la vez flexible, lo que permite realizar el modelado de una forma estructural y a la vez el flujo de datos en el hardware. Las ventajas que ofrece el uso del VHDL son:

- Permite el diseño, modelado y comprobación del sistema, sintetizando hardware en bajo nivel.

- Permite dividir el diseño del hardware en unidades más pequeñas para su descripción.

- Los circuitos que se describen siguen una estructura de síntesis.

- Basado en un estándar IEEE STD 1076-1987, para que así pueda ser usado por toda la comunidad de ingenieros.

#### 2.2.8. Niveles de abstracción

La abstracción es un modelo simplificado del diseño de hardware, una abstracción de alto nivel contiene sólo los datos más vitales. Por otro lado, una abstracción de bajo nivel es más detallada.

Los niveles de abstracción se emplean para clasificar modelos HDL según el grado de detalle y precisión de sus descripciones [11]. Los niveles de abstracción descritos desde el punto de vista de simulación y síntesis del circuito pueden definirse como sigue:

- Funcional o algorítmico: Se refiere a la relación funcional entre las entradas y salidas del circuito o sistema, sin hacer referencia a la realización final (implementación).

- Nivel de Transferencia de registros (RTL): Consiste en la partición del sistema en bloques funcionales sin considerar a detalle la realización final de cada bloque

Lógico: El circuito se expresa en términos de ecuaciones lógicas o de compuertas.

# 2.2.9. Estilos de descripción de hardware

El lenguaje VHDL presenta tres estilos de descripción que dependen del nivel de abstracción.

a. Descripción comportamental: Describe el comportamiento de las salidas del circuito con respecto a las entradas, en este estilo de descripción de hardware no se proporciona información de cómo estará conformado el circuito.

```

2 : -- Module Name: mux 4to1 sequential statement (if-elsif-else)

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

5

6

8 Port (

9 :

a,b,c,d : in std logic;

s : in std_logic_vector(1 downto 0);

f : out std_logic

10

11 :

12 ;

13 \(\hat{\to}\) end mux_4tol_iee;

15 architecture Behavioral of mux 4tol iee is

16 | begin

17 🖯

mux: process(a,b,c,d,s)

18 :

begin

19 🖯

if (s="00") then

20

f <= a;

21 :

elsif (s="01") then

22

f <= b;

23

elsif (s="10") then

24

f <= c;

25

else

26

f <= d;

27 🖨

end if;

end process mux;

29 end Behavioral;

```

Fig. 6. Descripción comportamental de un multiplexor.

Descripción flujo de datos: Especifica el circuito mediante un conjunto de expresiones booleanas concurrentes, en este estilo se describe el flujo de la información.

```

-- Project Name: mux 2to1 - simple signal assignment statement

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

7 - entity mux_2tol_ssas is

Port (

9

a : in std logic;

b : in std logic;

10

11

s : in std logic;

f : out std logic

12

13

);

14 \(\hhcappa\) end mux_2tol_ssas;

16 \stackrel{\cdot}{\ominus} architecture Behavioral of mux_2tol_ssas is

17

begin

18

f <= ((not s) and a) or (s and b);

19 🗀 end Behavioral;

```

Fig. 7. Descripción del flujo de datos de un multiplexor.

Fuente: Elaboración propia.

c. Descripción Estructural: Especifica el circuito describiendo distintos módulos y las conexiones entre estos.

Fig. 8. Descripción estructural de un multiplexor.

#### 2.3. Marco conceptual

#### 2.3.1. Controlador de radar

Para el diseño del controlador de radar ionosonda en primer lugar se comprenderá el protocolo de comunicación SPI dado que será el medio de interfaz de comunicación entre el embebido y el FPGA.

Mediante la descripción de hardware se define la interfaz SPI en modo A, el cual hace la lectura del data frame de n bits, para modo práctico de este ejemplo usamos 16 bits cuando la polaridad del CLK inicia en bajo (CPOL=0) y luego se detecta la fase del CLK en flanco de subida (CPHA=0).

# **CONTROLADOR SPI (ESCLAVO MODO 0)**

Fig. 9. Protocolo de comunicación SPI.

Fuente: Elaboración propia.

Posteriormente el data frame de 16 bits se divide en tres salidas llamadas W/R(1 bit), ADDRESS(6 bits), DATA(7 bits) y por medio de la señal W/R se almacenan los datos en el bloque mapa de registros.

Estos registros contendrán la configuración del barrido de frecuencias de 1 a 25 MHz, ancho de pulso, Ipp, código, repeticiones. A continuación, se muestra la tabla 1 donde se aprecia cada uno de los registros y sus respectivas longitudes de palabras, esta tabla la tenemos como referencia para el diseño del controlador de radar.

|             |            |          |          |               |               |               | P/W           | P/W           |     |

|-------------|------------|----------|----------|---------------|---------------|---------------|---------------|---------------|-----|

| CONTROL     | _ ·        | -        | -        |               | -             | -             | START         | RST           | \$0 |

|             |            |          |          |               |               |               | 0             | 1             |     |

|             | P/W        | ₽W       | ₽W       | BW            | ₽₩            | ₽₩            | PW            | P/W           |     |

| FREQ 1      | FREQ7      | FREQ6    | FREQ5    | FREQ4         | FREQ3         | FREQ2         | FREQ1         | FREQ0         | \$0 |

|             | 0          | 0        | 0        | 0             | 0             | 0             | 0             | 0             | •   |

|             |            |          | ₽W       | ₽₩            | ₽₩            | ₽₩            | ₽W            | P/W           |     |

| FREQ_2      | -          | -        | FREQ13   | FREQ12<br>0   | FREQ11<br>0   | FREQ10<br>0   | FREQ9         | FREQ8         | \$0 |

|             | P/W        | P/W      | P/W      | ₽₩            | P/W           | ₽₩            | P/W           | P/W           |     |

| PULSE WIDTH | 1 PULSE-W7 | PULSE-W6 | PULSE-W5 | PULSE-W4      | PULSE-W3      | PULSE-W2      |               | PULSE-W0      | \$0 |

|             | 0          | 0        | 0        | 0             | 0             | 0             | 0             | 0             | •   |

|             | ₽₩         | ₽W       | ₽W       | ₽₩            | ₽₩            | ₽₩            | ₽W            | ₽₩            |     |

| PULSE WIDTH |            |          |          | PULSE-W12     |               | PULSE-W10     |               | PULSE-W8      | \$0 |

|             | 0          | 0        | 0        | 0             | 0             | 0             | 0             | 0             |     |

|             | ₽₩         | ₽₩       | R/W      | RW            | ₽₩            | ₽₩            | ₽₩            | P/W           |     |

| IPP_1       | IPP7       | IPP6     | IPP5     | IPP4          | IPP3          | IPP2          | IPP1          | IPP0          | \$0 |

|             | 0          | 0        | 0        | 0             | 0             | 0             | 0             | 0             |     |

|             | ₽₩         | ₽₩       | R/W      | ₽₩            | ₽₩            | ₽₩            | ₽₩            | ₽W            |     |

| IPP_2       | IPP15      | IPP14    | IPP13    | IPP12         | IPP11         | IPP10         | IPP9          | IPP8          | \$0 |

|             | 0          | 0        | 0        | 0             | 0             | 0             | 0             | 0             |     |

|             | ₽₩         | P/W      | R/W      | RW            | ₽₩            | ₽₩            | ₽₩            | ₽₩            |     |

| IPP_3       | IPP23      | IPP22    | IPP21    | IPP20         | IPP19         | IPP18         | IPP17         | IPP16         | \$0 |

|             | 0          | 0        | 0        | 0             | 0             | 0             | 0             | 0             |     |

|             | P/W        | P/W      | P/W      | RW            | RW            | RW            | ₽W            | P/W           |     |

| CODE _1     | CODE7      | CODE6    | CODE5    | CODE4         | CODE3         | CODE2         | CODE1         | CODE0         | \$0 |

|             | 0          | 0        | 0        | 0             | 0             | 0             | 0             | 0             |     |

|             |            |          |          | 0             |               |               |               |               |     |

|             |            |          |          | ₽₩            | RW            | ₽₩            | ₽₩            | P/W           |     |

| CODE _16    | -          | -        | -        | CODE 124<br>0 | CODE 123<br>0 | CODE 122<br>0 | CODE 121<br>0 | CODE 120<br>0 | \$2 |

|             | RW         | ₽W       | P/W      | ₽₩            | P/W           | ₽₩            | RW            | ₽₩            |     |

| REPEAT      | REPEAT7    | REPEAT6  | REPEAT5  | REPEAT4       | REPEAT3       | REPEAT2       | REPEAT1       | REPEAT0       | \$2 |

|             | 0          | 0        | 0        | 0             | 0             | 0             | 0             | 0             |     |

Tabla 1. Mapa de registros del generador de señales de radiofrecuencia.

Fuente: Elaboración propia.

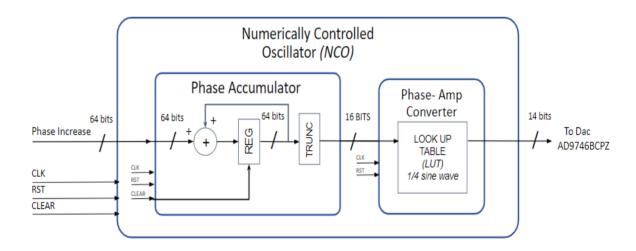

# 2.3.2. Oscilador controlado numéricamente (NCO)

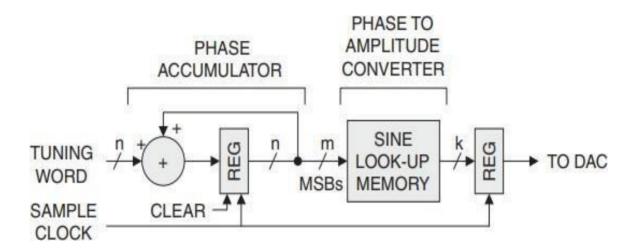

El NCO para generar una onda sinusoidal requiere de la palabra de sintonización de n bits o también llamado incremento de fase de n bits, dicha señal de entrada nos permite determinar la frecuencia de la salida de onda sinusoidal. El incremento de fase se expresa en un formato llamado medición de ángulo binario (BAM), en el que el bit más significativo (MSB) de la palabra representa 180º, el siguiente bit representa 90º, y así sucesivamente.

El NCO comprende un acumulador de fase, un convertidor de fase a amplitud y registros. En el acumulador de fase, se ingresa la señal de incremento de fase a la salida de la suma acumulada, implementada como un sumador seguido de un registro (REG), esto produce una fase de aumento uniforme, incrementada a la velocidad del reloj del sistema. Luego la suma acumulada (MSBs) se envía a un convertidor de fase a amplitud, que es una tabla de búsqueda que produce un valor de k bit también seguido de un registro que representa la amplitud de la onda sinusoidal en la fase de entrada [12].

Fig. 10. Diagrama de bloque del NCO [12].

Teniendo los valores de los parámetros de frecuencia interna del FPGA, frecuencia de la onda senoidal, incremento de fase y ancho de fase, entonces la frecuencia de la onda senoidal se puede representar como:

$f_{clk}$  = Frecuencia interna del FPGA

$f_{out}$  = Frecuencia de la onda senoidal

$\Lambda\theta$  = Incremento de fase

$2^{B_{\theta(n)}}$  = Ancho de fase

$$f_{out} = \frac{f_{clk} x \Delta \theta}{2^{B_{\theta(n)}}}$$

(2.6)

Para generar una onda senoidal con una frecuencia de 1 MHz, el incremento de fase requerido para generar dicha onda es el siguiente:

$$\Delta\theta = \frac{f_{out} x 2^{B_{\theta(n)}}}{f_{clk}}$$

$$\Delta\theta = \frac{1_{Mhz} x 2^{14}}{250_{Mhz}}$$

$$\Delta\theta = 65.036$$

Al incremento de fase se debe aumentar un valor de 0.5 y luego truncar a un número entero e introducirlo en la ecuación (4) dando la siguiente frecuencia de salida, que puede ser validada por los instrumentos que se cuenta en el laboratorio de Investigación y Desarrollo e Innovación (IDI) ubicado en el Radio Observatorio de Jicamarca.

$$f_{out} = \frac{f_{clk} x \Delta \theta}{2^{B_{\theta(n)}}}$$

$$f_{out} = \frac{250_{Mhz} x 66}{2^{14}}$$

$$f_{out} = 1.00708_{Mhz}$$

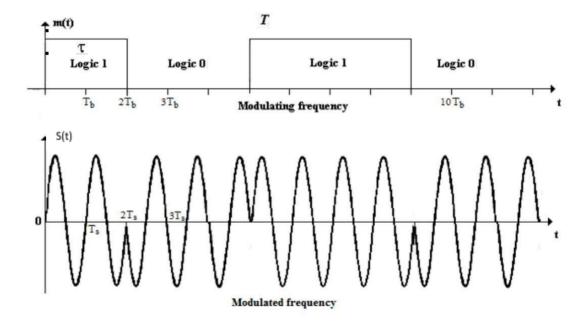

#### 2.3.3. Modulación BPSK

La modulación BPSK es una modulación por desplazamiento de fase de dos estados, donde la fase de la portadora se establece en 0 o π según el valor de la señal moduladora. La señal moduladora m(t) se define como una secuencia binaria que se multiplica con una portadora sinusoidal c(t), obteniendo así la

señal modulada BPSK. Cuando la señal de salida del modulador m(t) se encuentra en un estado '1' la señal modulada se ve exactamente como la portadora con 0º de fase inicial, mientras que, si se encuentra en un estado "0", la señal modulada tiene una portadora con fase inicial de π, la modulación BPSK se representa en la ecuación 2.7.

$$s_{i}(t) = \begin{cases} s_{1}(t) = -A\cos(2\pi f_{c}t), & \text{if } 0_{T} \\ s_{2}(t) = +A\cos(2\pi f_{c}t), & \text{if } 1_{T} \end{cases}$$

(2.7)

En la modulación BPSK, la señal transmitida es s(t) = m(t)c(t), donde 0 < t < Tb

Cabe mencionar que T es el tiempo de duración del pulso codificado, t es la duración de los sub pulsos y la fase de cada sub pulso es modificable para que varíe entre 0 y π. En esta modulación una de las características fundamentales es que se puede obtener su relación de compresión con la ecuación 2.8.

$$N = T / t \tag{2.8}$$

Fig. 11. Modulación por código de desplazamiento de fase (BPSK) [14].

Para el diseño del generador de señales de radiofrecuencia que operará al transmisor de radar ionosonda se requiere de un modulador de BPSK digital el cual se implementará en descripción de hardware VHDL en el software Vivado.

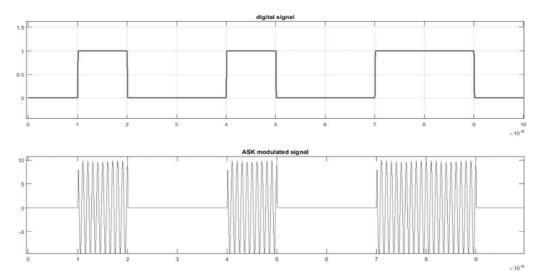

#### 2.3.4. Modulación OOK

La modulación de desplazamiento de amplitud binario (On Off Keying) es un caso particular de la modulación ASK. Este tipo de modulación tiene un comportamiento de conmutación ya que cuando se ingresa una señal binaria unipolar f(t), la cual, si la señal del mensaje es "1", entonces la salida será una señal sinusoidal, si el mensaje la señal es "0", entonces la salida será 0. Su función se representa en la siguiente ecuación 2.9.

$$f_{ASK}(t) = f(t)\cos(\omega_c t) \tag{2.9}$$

- si  $f(t) = 0V \Rightarrow f_{ASK}(t) = 0$

- si  $f(t) = AV \Rightarrow f_{ASK}(t) = A\cos(\omega_c t)$

A continuación se muestran los gráficos de la modulación OOK.

Fig. 12. Modulación de desplazamiento de amplitud binario (OOK) [13].

La modulación OOK será utilizada para la generación del barrido de frecuencias de 1 a 25 MHz que estarán sincronizados con la señal de GPS de 10Mhz e iniciará el envío de las señales de radiofrecuencia cuando la entrada trigger detecta un flanco de subida (*rising edge*).

#### 2.4. Definición de términos básicos

- ROJ: Radio Observatorio de Jicamarca.

- IGP: Instituto Geofísico del Perú.

- UMLCAR: Centro de Investigaciones Atmosféricas de la Universidad de Massachusetts Lowell.

- GNSS: Sistemas de posicionamiento global basados en satélites.

- USRP: Universal Software Radio Peripheral.

- FPGA SoC: Arreglos de puertas programables en campo de sistema en chip.

- Zynq SoC: Son dispositivos de la familia Xilinx que integran un FPGA y un procesador.

- VHDL: Es un lenguaje de descripción de circuitos electrónicos digitales que utiliza distintos niveles de abstracción.

- Ip Cores: Son diseños de hardware de uso libre.

- RTL: Nivel de Transferencia de registro.

- NCO: Oscilador controlado numéricamente.

- BPSK: Modulación de desplazamiento de fase binario.

- OOK: Modulación de desplazamiento de amplitud binario.

- lonogramas: Son diagramas generados por ionosondas, que nos permiten medir las frecuencias críticas de cada capa y las alturas virtuales.

- Altura virtual (HV): Estas alturas son mayores que la altura real y son generadas por los ionogramas.

- FoF2: Frecuencia crítica de la capa F2.

- IPP: Período entre pulsos emitidos por el generador de señales.

- HF: Alta frecuencia.

- SNR: Relación señal / ruido.

#### III. HIPOTESIS Y VARIABLES

#### 3.1. Hipótesis general e hipótesis específicas

## 3.1.1. Hipótesis general

Con el diseño e implementación de un generador de señales de radiofrecuencias basado en FPGA SoC se operará un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca.

# 3.1.2. Hipótesis específicas

- Hipótesis específica 1: Con el diseño e implementación de un generador de señales de radiofrecuencias basado en FPGA SoC se podrá sincronizar la señal de GPS en un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca.

- ❖ Hipótesis específica 2: Con el diseño e implementación de un generador de señales de radiofrecuencias basado en FPGA SoC se podrá emitir un barrido de frecuencia en un transmisor de radar ionosonda en el Radio Observatorio de Jicamarca.

- Hipótesis específica 3: El diseño e implementación del circuito modulador de señales de radiofrecuencias basado en FPGA SoC permitirá realizar modulación BPSK y OOK.

## 3.2. Definición conceptual de variables

### 3.2.1. Variable independiente

Diseño e implementación de un generador de señales de radiofrecuencia

basado en FPGA SoC: Un generador de señales es aquel dispositivo

electrónico que genera patrones de señales periódicas o no periódicas y en

este trabajo de investigación se generan de manera digital.

a. Dimensión 1:

Sintetización de hardware: La sintetización de hardware es el proceso

de generación de una representación en puertas lógicas de una

descripción hardware (VHDL o Verilog).

Indicador 1: Simulaciones con el Test bench.

Indicador 2: Pruebas en el laboratorio

3.2.2. Variable dependiente

Operación de transmisor de radar ionosonda en el Radio Observatorio de

Jicamarca: Los transmisores de ionosonda son radares HF que transmiten

pulsos electromagnéticos desde un determinado punto de la Tierra hacia la

ionosfera.

a. Dimensión 1:

Sincronismo: En telecomunicaciones el sincronismo es muy utilizado

para que diversos equipos de un mismo sistema puedan compartir la

misma señal de reloj y mandar información de forma que todos los

equipos estén sincronizados.

**Indicador 1:** Desfase entre la señal generada y la señal de GPS.

a. Dimensión 2

52

Análisis espectral de las frecuencias: El análisis espectral de

frecuencias mide y traza la potencia de la señal en un rango de

frecuencias determinado para ello se utiliza el instrumento analizador de

espectro.

Indicador 1: Verificación del barrido de frecuencias con el analizador de

espectro.

3.3. Operacionalización de variables

3.3.1. Variable independiente